#### **Department of Electrical and Electronics Engineering**

#### **Regulation 2021**

II Year – IV Semester

**EC3402- Linear Integrated Circuits**

## EE 8451 LINEAR INTEGRATED CIRCUITS AND APPLICATIONS

## UNIT . I TC FABRICATION :

Ic clamitication, bundamental ob monoLithic Ic technology, epitanial growth, masking and etching, diffusion of impurities, Realisation of monolithic Ics and packaging, Fabrication ob diades, capacitance, resistance, FETS and PV cell.

## Introduction : -

The integrated circuit or Ic is a miniature low cast, electronic circuit consisting of active and parrive components that are irreparably joined together on a ringle crystal chip ob silicon. 1 dishlaiter

## Advantages:

- 1) Miniaturization and hence increased equipment density.

- 2) cost reduction due to batch processing.

- 3) Increased system reliability due to elimination

- 86 soldered joints.

- 4) Improved tunctional perbormance.

- 5) Matched devices.

- 6) Increased operating speeds.

- D Inc Reduction in power consumption

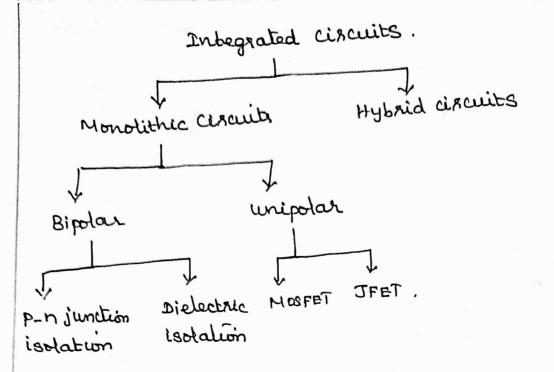

#### claribication :-

- 1) Digital Ics.

- li) Linear Ics.

2) Two disberent Ic Technology namely,

1) Monolithic Technology.

2) Hybrid Technology.

#### Monolithic Technology:

and parrive elements and their interconnections are manubactured into or on top to a single chip of silion.

suitable for identical circuits are required in very large anantitues and hence provides lowest per-unit cost and highest order of reliability.

## Hybrid Technology :-

Separate component parts are attached to a ceramic substrate and interconnected by means ob either metallization pattern or wire bonds. More suitable for small anantity curtom viscuits.

Bared upon active devices, Ics classified as Bipolar (using BJT) unipolar (using FET).

Fig: clarribication of Ics.

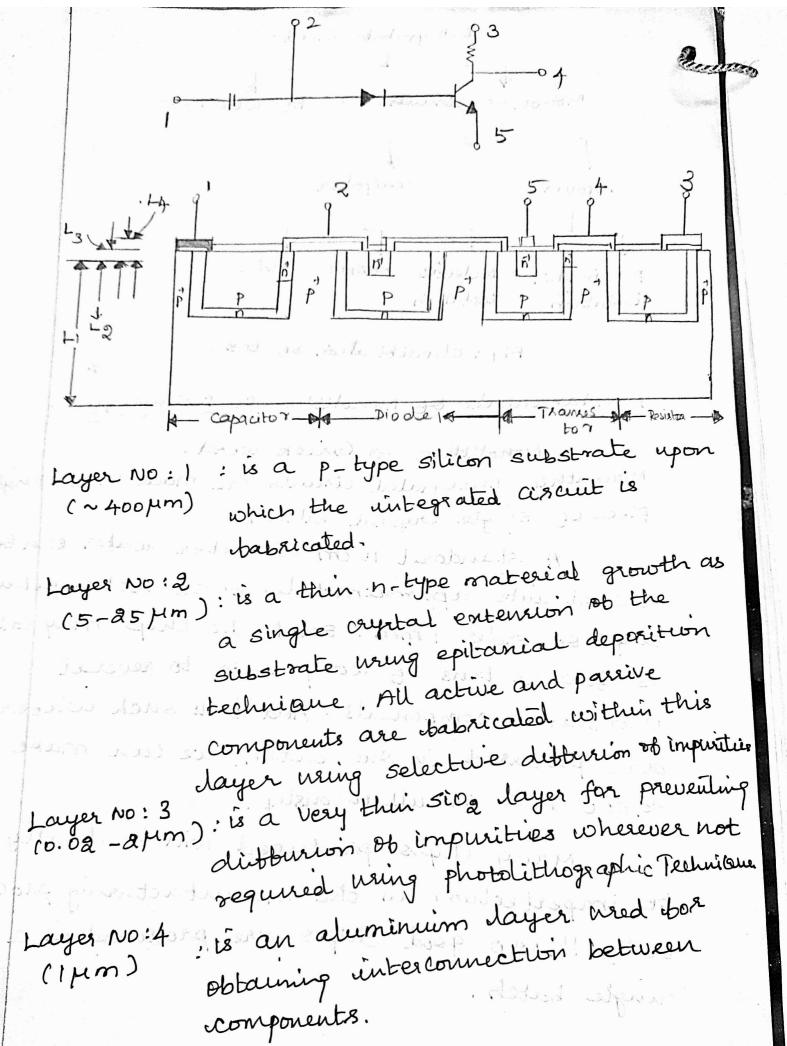

Fundamentals 06 Monolithèc Ic Technology: -

Monolithic -> Greek word.

Monolithic Integrated circuits are made in a single Piece of single crystal silicon.

A standard 10 cm diameter water can be divided into approximately 8000 rectangular chips 06 sides 1 mm. Each Ic chip may contain as few as tens 06 components to reveral thousands components. And it is such waters thousands components. And it is such waters are processed in one batch, we can make 80,000 Ics rimultaneously.

Many chips produced will be baulty due to imperbecturing in the manubacturing process. to imperbecturing and chips are produced in a only 16,000 good chips are produced in a ringle batch.

The basic processes used to babricate Ics using silicon plannar Technology can be bollons:

- 1. silicon waber (substrate) preparation

- 2. Epitanial growth

- 3. onidation

- 4. Photolithography

- 5. Diffusion

- b. Ion implantation

- 7. Isolation Technique

- 8. Mettallization

- 9. Assembly processing and packaging

## 1) Silicon water preparation:

The bollowing steps are used in preparation ob si-wabers

- 1. Crystal growth and doping

- a, Ingot trimming and grinding

- 3. Ingot slicing

- 4. Water Polishing and etching

- 5. waber cleaning.

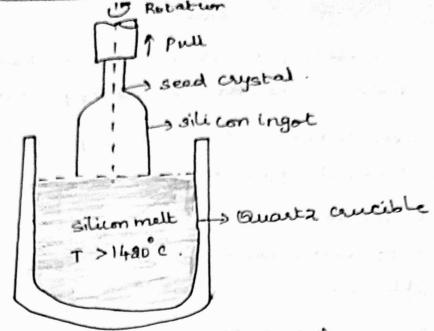

Czochralski crystal Growth process: It is often used for producing single crystal silicon ingots. The perty highly puribled (99.9999) Polycystalline silicon together with an dopant is put in a Quartz Crucible and then placed in a burnace.

Czachralski orystal Growth.

Silicon Waber, D=10, 1&5, 15 cm showing that orientation

the first first plant process of the

appet mouther smuller separations

=) The material is then heated to a temperature of 1480°C.

2) A small single crystal rod of silicon called seed crystal is disped into the called seed crystal is disped into the silicon melt and slowly pulled out. It silicon melt and slowly pulled out. It brings solidified mass of silicon with the brings solidified mass of silicon with the same crystalline structure as that of seed crustal.

2) During the process, the seed crystal and the crucible are rotated in opposite directions the crucible are rotated in opposite directions in order to produce ingots of circular cross in order to produce ingots of circular cross section. Ingot diameter 10 to 15 cm, length loom section. Ingot diameter 10 to 15 cm, length loom

2) The top and bottom portuins of the ingot are cut-off and the ingot surface is ground are cut-off and the ingot surface (D =10,18.5,15 cm) to produce an exact diameter (D =10,18.5,15 cm)

2) The ingot is sliced wing a stainless steel with industrial diamonds saw blade with industrial diameter cutting embedded into the inner diameter cutting embedded into the circular wabers or slices. edge. This produces circular wabers or slices.

2) The orientation beat postum serves as a webut reperence plane.

=> The obtained dicon waters under 90 a number of polishing steps to produce a flat number of polishing steps to produce a flat surbace.

a) After all the Ic fabrication processes are complete then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 8000 rectangular then waters are sawed into 100 to 100 to 8000 rectangular then waters are sawed into 100 to 100

a single Ic and contain hundreds of components.

## @ EPIMXIAL GROWTH!

PCH2+B2+6.

pe HCL

Epitany means, arranging atoms in single crystal substrate, crystal fashion upon a single crystal substrate, so resulting layer is an entermion of the substrate crystal structure.

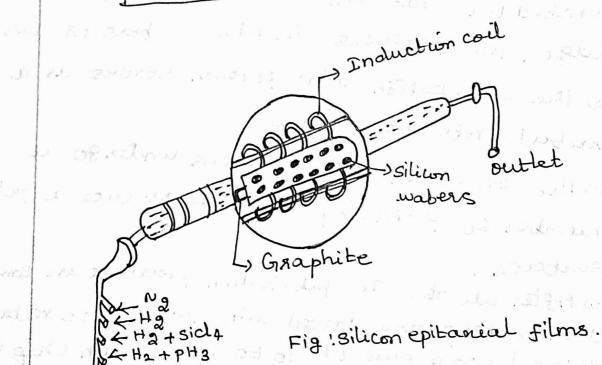

2) The process is carried out in a reaction chamber consisting of a long cylindrical Quarte tube encircled by an RF induction coil.

2) The silicon waters are placed on a rectangular graphite rod called a boat.

2) This boat is then placed in the reaction Chamber where the graphite is heated inductively to a temperature 1200°C.

=> Various gases required for the growth of desired epitanial layers are introduced into the system through a control console.

sich + and lavoc si + 4Hd.

Sign has the property of preventing the disburion ob all impuritions through it. It serves 2 purposes ission is an entremely hard protective conting and unabbected by almost all reagents except hydrofluoric vacid.

11) By selective etching Sion, dibbuseon of impuitues through carebully debined windows in the sion can be accomplished to babricate various components. Silicon wabers are stacked up in a Quartz book and then inserted into Quartz burnace tube. The Si-wabers are raised to a high temperature in the range ob 950 to 1115°c, and exposed to a gas containing of or Hao or both.

Si + 8 H& O - SiOg + 8 Hg.

Thickness of onide layer is 0.02 to 2 pm.

# 4) Photolithography: -

Photolithography is wed to produce microscopical small circuit. It uses X-ray or electron beam litrographic techniques, to produce device dimension down to sub-micron range <1 µm).

It involves two processes

- Dualting of a photographic mask,

- 2) Photo etching.

ci) Making ob a photographic Mask:

Involves the bollowing sequence of operations is Initial artwork.

ii) Reduction: ( see a planting of

Initial artwork is done at a scale several hundred times larger than the binal dimensions hundred times larger than the binal dimensions of the binished monolithic vircuit. Drawings are made magnitud and other by a bactor of soo. The width of one mil is magnitud to a width of soo mils, i.e 1.8 cm. so, finished monolithic chip of area somil x somil, the monolithic chip of area somil x somil, the artwork will be made on an area of about

The artwork should not contain any line drawings but alternate clear and opaque regions. This is accomplished by the use of red clear Mylar coated with a sheet of red clear Mylar coated with a sheet of red photographically opaque mylar (Rubylith), photographically opaque mylar (Rubylith), photographically opaque mylar (Rubylith), machine known as coordinatograph, machine known as coordinatograph,

This subylith pattern of individual mask is photographed and then reduced in steps by a bactor of 5 or 10 several times steps by a bactor of 5 or 10 several times to binally obtain the exact image size. The to binally obtain the exact image size. The binal image repeated many times in a matrix binal image repeated many times in a matrix of that many so that many Ics will be produced in array so that many Ics will be produced in one device process.

20

The photo repeating is done with a step and repeat commera. This is an imaging device with a photographic plate on a movable platform. Between exposure the plate is moved in equal steps so that successive images borm in an away.

when the emposed plate is developed, it becomes a master mask. Utraviolet radialism

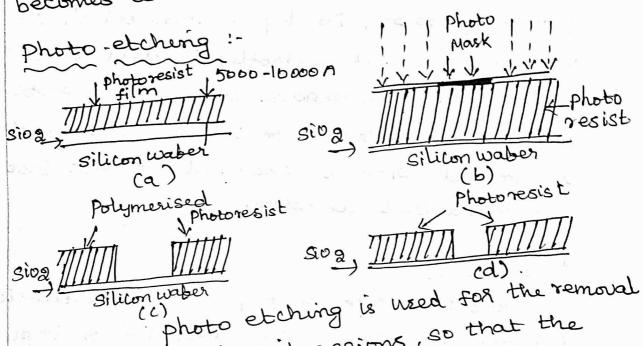

photo etching is used that the ob sion from desired regions, so that the desired regions, so that the desired impurities can be distrused. The desired impurities can be distrused. The waber is coated with a bilm of photogensitive waber is coated with a bilm of photogensitive emulsion (kodak photogensis k KPR). The emulsion (kodak photogensis k KPR). The thickness of the film is in the range of 5000-10000A

The mask negative of the desired pattern prepared by steps earlier is placed over the proposed by steps earlier is placed over the photoresist coated waber. This is now emposed to photoresist coated waber. This is now emposed to photoresist light, so that the kpr becomes ultraviolet light, so that the kpr becomes polymerized beneath the transparent regions the the mask.

The mask is then removed and the waber is developed using a schemical (trichloreethylene) which dissolves the unemposed unpolymerized regions on the photoresist and leaves the Pattern f.3(c).

The polymerised photorerist is next bired on cured, so that it becomes immune to certain chemicals called etchants wed in subsequent processing steps. The thip is immersed in the etcherig solution of hydrofluoric acid, which removes the sing brom' the areas which are not protected by KPK: Abter detburion of impurities, the photoresist is removed with a chemical solvent (hot Hason) and mechanical abrasion.

## Diffusion!

Another important process in the babrication ob monolithic Ics is the dibburion of impurities in the silicon chip. This was a high temperature turnace having a that temperature probile over a wretul length (about 20" length).

A suartz boat containing about 20 cleaned waters is purhed unto the hot some with temp maintained at about a 1000°C.

Components such as Baba (Boron Onide), Bcl3 (Boron chloride) are used for Boron and Paos (Phosphorons pentaoxide) and Podz (Phosphorons oxychloride) are used as sources of phosphosons.

A carrier gas such as dry onggen on hitrogen is normally used for sweeping the improvity to the high temperature zone. The depth ob disturion depends upon the time of dibburion which normally entends to a hours.

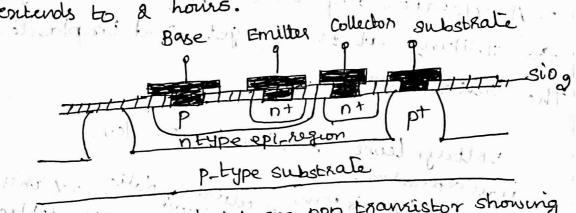

cross section of an nph transistor showing Curried junction, protiles as a result ab lateral diffusion.

Ion Implantation:

.) This technique ned to introduce impurities

into a silicon water.

It is the process, the long of a particular impurity. 08 dopkant material are accelerated by an electric tield to a very high velocity and lodge the dopant within the semiconductor material.

=) A gas containing the derived impurity is ionized inside an ion source. => The ion's are generated and directed from the source in a diverging beam and boccured. Then park through a mass eparator,

testions in ferry of traders.

=> Mars separator directs only the tons of the desired dopard. =) Second lens focuses this bearn, then powered through an accelerator. =) Accelerator imparts the required energy for striking at the target and implanted in the silicon water. voltage level: 20kV to: 250 kV. heavier ions Accelerator platie y anie Hays separator plates. second electrical lighter ions In beam -> First electrical Jaid Division chambes Advantages: DAccurate control over doping 2) Very good reproducibility 3) Room temp process. Limitations !-1) Higher temperature is required bor avoid the crystal damage. 2) Possibility of dopant implanting through varions dayers ob waters.

Each of the water processed contains several hundred chips, each being a complete circuit. so these whips must be separated and individually Packaged. A common method called scribing and cleaving used box separation makes use ob a diamond tipped tool to cut lines unto the surbace of the water along the rectangular grid Separating the individual chips.

The water is bractured along the scribe lines and the individual chips are physically reparated. Each chip is then mounted on a ceramic water and attached to a suitable package.

Three dibberent package contigurations are i) Metal can Package - available in 8, 10, 12 leads.

- 2) ceramie that package -> costly due to babrication process

- 3) Dual in-line (ceramic on plantic type) package.

> 8,14,16 leads (0x) 24 0x 36 0x 42 leads.

I Advantage: Best hermetic sealing. 14 lead bersion of Hat package Ceramic over 70-5 Metal Package kovag eyelet Glass Leads (10) -

En l

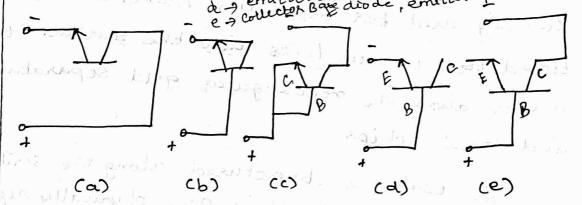

#### Monolithic Diodes:

Figure shows the dibberent possible connections by which a transistor could be utilized as a diode c, d, e are popular, collector short circuited to the base diode, collector open.

C -> emitter Base diode, collector open.

d -> collector Base diode, emitter open circuited.

cross section view ob various diade structure.

|                           |              | 13.1   |           |      |          |

|---------------------------|--------------|--------|-----------|------|----------|

| characteristic            | (0)          | (P)    | ලා        | CD   | (e)      |

|                           | VCB 20       | VCE 20 | NEB =D    | 1c=0 | JE =0    |

| Breakdown voltage (volts) | -42.7(3. 15) | 7      | 55        | 7    | 55       |

| storage time, (n sec)     | 9            | 100    | 53        | 56   | 85       |

| Forward vollage (volts)   | .85          | • 92   | •94       | -96  | • 95     |

| rd                        | · ·          | 3-1-   | 77.1 16.1 | k    | <u> </u> |

The diode a is ureful for high speed, lowert storage time, lowest borward voltage drop.

-> Diode b & d ured for stored charge device and high speed turn-obb ob the transistor.

2) Diode c & e have highest breakdown voltage.

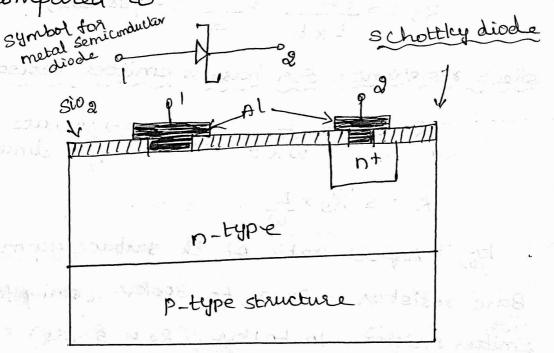

#### schottky Barrier Diode :-

Aluminium is a p-type impurity in silicon. When it is used to make a contact with n-type si, that contact is ohmic and no pn function is boomed.

=) This is done by making nt diffusions in the n-regions near the surborce where Al is deposited.

a metal semiconductor diode is borned

=> Fig shows two contacts, contact 1 is a schottly barrier and contact & is an ohmic contact.

2) The contact potential between the semiconductor and the metal creates a barrier to the blow ab conduction electrons from semiconductor to metal.

2) Forward biasing the junction lowers this barrier and permit electron blow from semiconductor to metal where electrons are abundant. Hajority currier electrons carry current in a schottly diade.

=) Schottley diodes has less borward voltage (03v) compared to the Ph diode  $(V_n = 0.6v)$ .

Strebol for

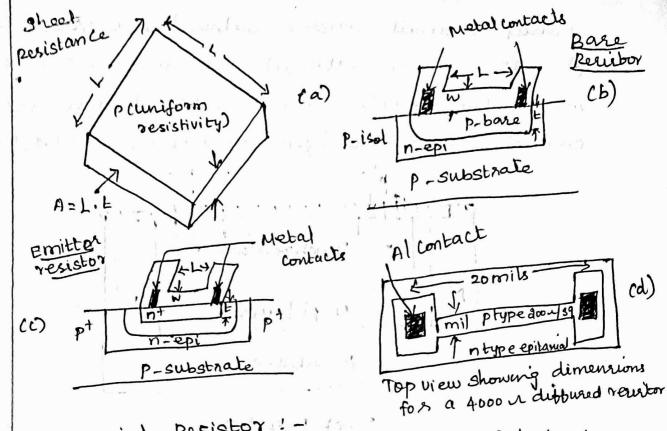

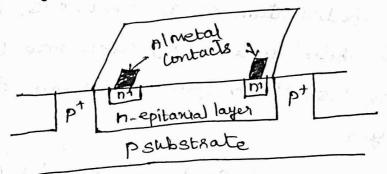

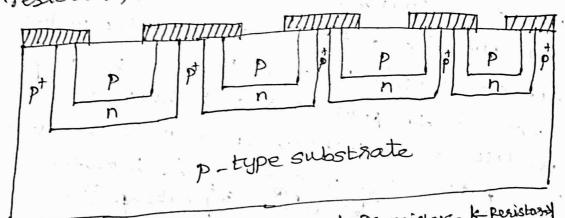

#### Integrated Resiston: (Fabrication of R)

- 4 dibberent methods

- roteized Resistor

- 2) Epitanial Resistor

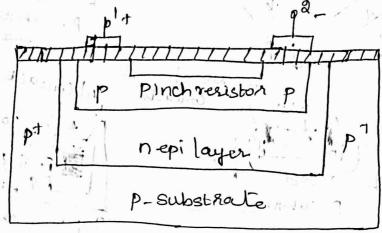

- B) Pinched Pesistor

- 4) Thin bilm Pesiston.

#### Diffused Resiston: -

Resistant is boomed in one of the isolated regions of epitamial layer during base on emitter diffusion, icommon to bipolar transistor babrication. Small range of resistances possible.

#### Sheet Pesistance (Rs):

consider the Souare LXL ob a material, resistivity P, thickness t, cross sectional Area A A = LXt. Resistance ob this sheet ob material

$$Rs = \frac{PL}{L \times E} = \frac{P}{E} ( \sqrt{souare})$$

sheet resistance for base & emitter resiston:

not bedough

Hw - Aspect vatio of the surbace geometry.

Base resistor: 20 r to 300km. (easily fabricated)

Emitter reristor: 10 to 1 km, (Rs is 51/5Q).

Epitanial Resistor! Large value of resistance possible by base or emitter resistor achieved by using n-epitamial Collector region. Rs is 1 to 10 km/se.

The sheet resistivity of a semiconductor region Pinched Pesiston con be increased by reducing its ettecture crosssectional area. This technique is used to achieve a high value Ob sheet resistance brom the ordinary base dittured resistor. Peristance: Mr in small ara. In the big, no current can flow through the n-type material (dark region) due to the diode at Contacto in the reverse direction.

=) only a small reverse saturation current can oflow through n-material. By creating this n-typin region, the abbective cross sectional area for the conduction path has been reduced, R = 182 inches

Punch Resiston,

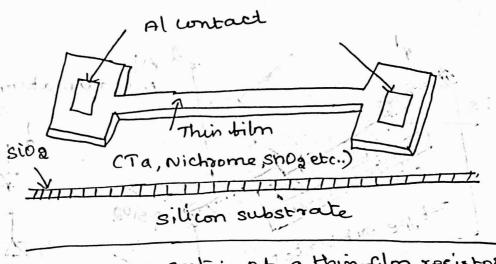

## Thin Film Resistor:

Vapour thin film deposition techniques used for the babrication of Ic resistors. A very thin metallic bilm usually of richrome (Nicr) of thickness less than I µm is vapour deposited on the sion layer.

using masked etching, descred geometry of this tilm is achieved to obtain suitable values of resistors. Ohmic contacts are made uring Al metallization.

Nichsome resistors are available with Rg 06 40 to 4001/savare, Resistance do to 50 km Obtained.

Advantages:

DIt has lesser and smaller pararitic components

and high brequency behaviour is better.

2) The values of thin-tilm resistors easily adjusted after babrication of by cutting a part of the resistor with a laser beam.

3) Low temp co-efficient, more stable.

Higher value of resistor obtained by depositing Tantalum over Sion layer. Disadventeres is additional process steps required bor babrication

cross section at a thin film resistor.

# Fabrication ob capacitance

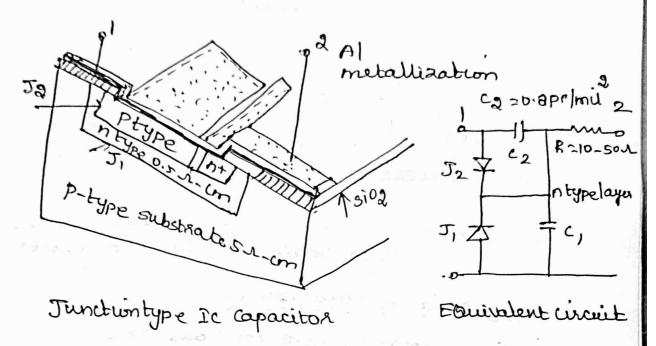

Two commonly used methods are

1) Junction capacitor

2) Mos and thin tilm capacitor.

#### D Junction capacitor !-

There are two junctions in this type of diffused capacitors. Junction Ja, if reverse bit produce the desired capacitonce. A parasitic capacitance C1 is inevitable due to the junction Capacitance C1 is inevitable due to the junction between n-type epitamial layer and the substrate

⇒) The substrate held at most negative point to minimize C1.

2) The value of the Co depend upon the area of the junction, impurity concentration of the n-type epitanial layer, voltage across the junction.

2) Ca is polarised, and obtained when Ig is R.B.

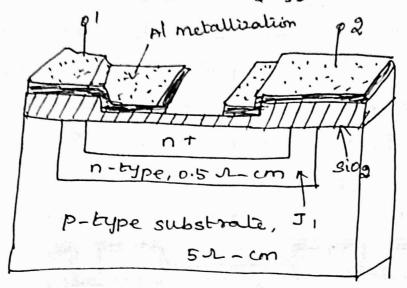

#### Mos and Thin tilm capacitor: -

=) It is borically a parallel plate capacitor with sion as the dielectric.

=) The heavily doped n + region bormed during emitter diffusion forms the lower plate.

=> Thin bilm 06 aluminium metallization bosms the upper plate 06 the capacitor with Sig as the dielectric

Advantage: Nonpolar.

Silicon Nitride CSi3NH) ured as a dielectric layer.

130

=>It requires a number of additional masking and deposition steps.

=) Aluminium or tantalum ired as capacitor plates and aluminium oride (Algo3) or tantalum oride (Tago5) as dielectric material.

Structure

Ecuivalent ciscuit of a Mos capacitar.

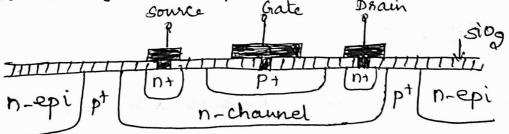

#### Fabrication ob FET :-

JFET Fabrication!

=> the epitamial layer which formed the collector of the BJT is used as the n-channel of the JFET.

=) The p+ gate is bormed in the n-channel by the Process as diffusion or ion-implantation.

=) The n+ regions bormed under the drawn and source contact regions to provide good ohmic contact.

P-type substrate

n-channel JFFT structure.

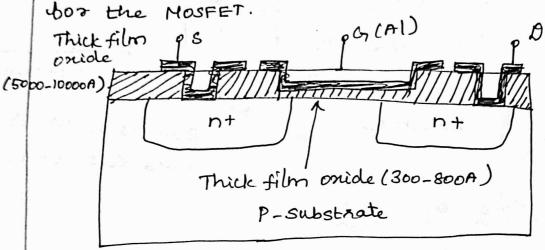

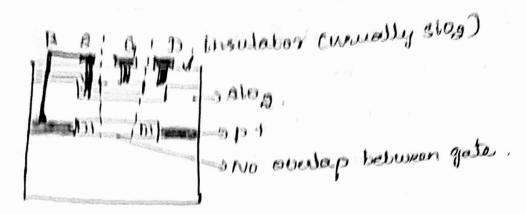

#### MOSFET Fabrication:

- i) Enhancement type

- 11) Depletion type

## N-channel Enhancement MOSFET !-

The metallic gate G is separated from the semiconductors channel by the insulating sign layer. The insulating layer of silecon dionida guies an extremely high input resistance (100 to 10151)

n-channel MOSFET.

VT -> 3 to 6V; power supply voltage: 18 V. > drawn supply

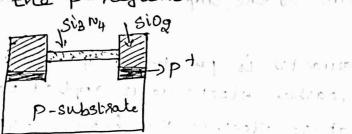

## use ob silicon Nitride (Si3 N4)

Signy sandwiched between two sing layers and provides necessary bourier to prevent impurities penetrating through sing layer.

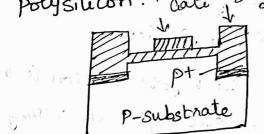

#### Polysilium Gate!-

Polyscrystalline silicon doped with Phosphorus is conductive and used gate electrode instead of aluminium.

n. olanovit. Trop others.

P-type waber.

=) with help of mask, source, gate and drawn included.

=> Signation region.

=) P+ impuritues are ion-implanted in the enposed

P-substrate.

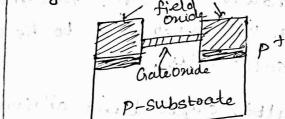

a) A thick sing layer called field oxede is grown wer the pt regions.

Sign4 is removed by selective etching and Sion layer (800 to 1000 Ab) is grown over the transmitor area.

Polysilicon is now deposited over the entire wabor.

The polysilicon gate is borned by selective removal of polysilicon.

Polysilicon. Polysilicon

Cate Sing

The n+ source and drawn regions are formed by ion implantation. The field oxide and the polysilium gete prevent the penetration of doponts below these regions. Drawn and source regions are borned.

I'v cell babalcation Procure !.

as Bebone making a silium waber, puro silicon is needed which needs to be recovered by reduction and purification of the impure vilicon disside in QUANTA 1

=> crushed quarte is put in a special burnace and then a carbon electrodo is applied to generate a high temperature electric and between the electrode and the silicon dionido. It reduces the onegen brom the silicon dionide and produces carbon dionide at the electrode and mother silicon, This molten silicon is 99% pure which is insubstituent to be used Mon Processing unto a solar celle.

In order to make multi-cupitalline silicon cells various methods exist !

- 1) Heat enchange Nethod.

- 2) electro magneto coesting

- 2) Directional evoliditication septem

=) During the costing of the ingots, silicon is often already pre-doped before slicing and selling the water disks to the manufacturers

. There p type and n type doping materials are mostly boron which has 8 electrons (3 valent) and phosphorous (5 electrons) used for n type doping

stepl water Preparation:

The starting material could the substrate ce a p-type silicon water prepared. water diameter: 10 cm, 0.4 mm (400 µm) thickness.

Resistivity: 101-cm, Concentration of acceptor atom, NA = 1.4 x10 atoms

400 pm. p-type substoate 101-cm resistivity, NA 21.4 X10 atomy

stepa: Epitanial Growth:

2) An n-type epitanial bilm (5-25pm) is grown on the p-type substrate. It becomes collector region of the transiston, element of the diode, distured capacitos.

2) All active & passève components are boibricated. 2) Peristivity is 0.1 to 0.5 1cm.

n-epi layer oil - 0.5 r-cm. 5-25 Mm. p-type substrate 101-cm.

steps: onidation

A Sion layer of thickness of the order of 0.00 to a form

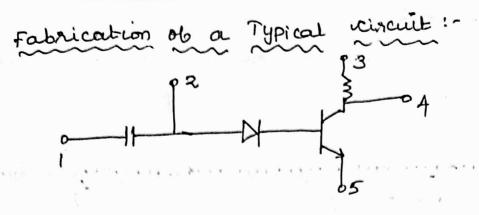

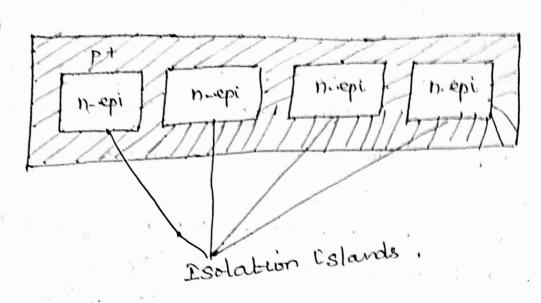

Step 4: Isolation Distrision!

En the given circuit, bour components have to be babricated. So, four islands are required and isolated. So, Sion is removed brom bive and isolated. So, Sion is removed brom bive dibberent places using photolithographic technique

2) Then heavy p-type distrission for a long time interval, so that p-type impurities penetrate the n-type epitanial dayer and reach the p-type substrate.

=) The concentration of NA = 5 × 10° cm³ in the region between isolation islands is lept higher region between isolation islands is lept higher than P-type substrates (NA = 1.4 × 10° atoms/cm)

Island 1 pt Island 2 pt Island 3 pt Island 4 y

pt n-epi n-epi n-epi pt

ptype substrate

step Base Dibbusion ..

=> A new layer of sion is grown over the entire water and a new pattern ob openings is bosmed using photolithographic Technique.

>> P-type impurities such as boron oire distured through the openings. It does not penetrate through n-layer into the substrate, This diffusion is used to born base region, of the transistor, resistor, anode of the diade, Tunction capacitors.

K-Transistor K- Periston to capaciton piode-

## step & Emilter Diffusion :-

DA new layer of sing is again grown over the entire water and selectively etched to open a new set of windows & n-type impurity (phosphorous) is differed. This booms transistor emitter & cathode region of idiode.

- 2) windons (w, we etc) also etched into n-region where contact is to be made to the n-type layer.

- => Heavy concentration of phosphonous (2 x 1000 cm3) doping causes a high degree ob damage to the Si-lattice, and making it semi- metallic.

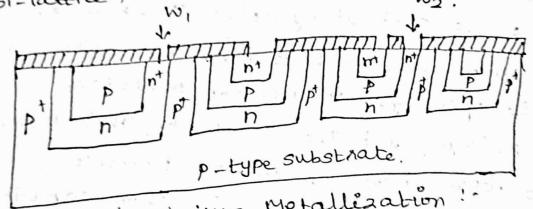

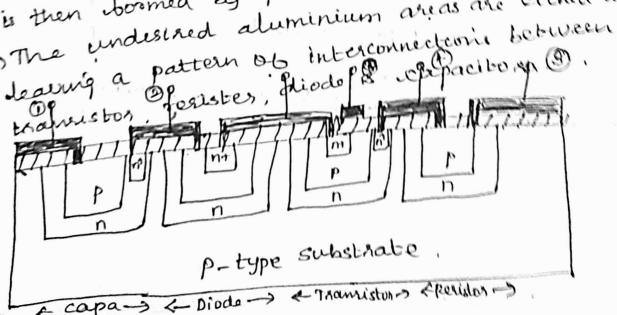

# step 7 Aluminium Metallization!

- =) A thun even coating ob aluminium is vacuum deposited over the entire surbace of the unbeg.

- =) The interconnection pattern between the components is then boomed by photo-serist techniques.

- =) The undestred aluminium areas are etched away

## UNIT-I De characteristics

- From the source

- In real op-amp, current is taken.

From the source into the op-amp inputs.

- 2) real op-amp dependent of temperature

Buy Mil For

- D.C. Characteristics are

- 1) Enput bias current

- a) Input obbset current

- 3) Input obbset voltage

- 4) Thermal drift.

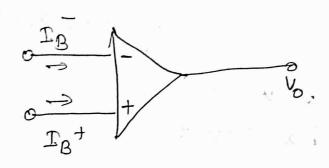

## 1) Input Bias current:-

- The op-ample input is a dibberential amplibies, made of BJT 08 FET.

- -) To supply current into the bares by the external circuit, the transistor. must be biased.

- In practical op-amp a small value of dc current is parred to the input terminals to bias the input transistors.

- The bare current entering into the inverting & non-inverting terminals

are IB and IB.

DIB & IB are not exactly early due to internal imbalances between the two inputs,

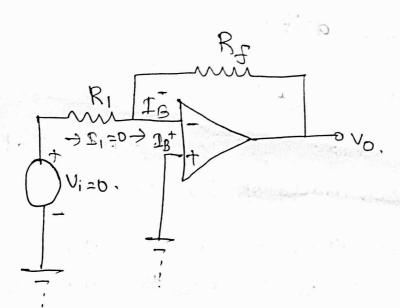

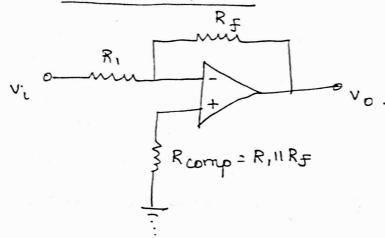

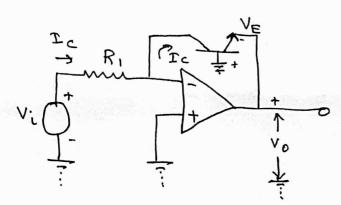

fig: 1 Input Bias current.

fig: 2. Inverting amplifies with bias currents.

$$D_{B} = \frac{D_{B}^{+} + D_{B}^{-}}{2}$$

FOR 741, a bi-polar op-amp the bias current is 50 on A or less.

FOR FET input op-amp bias currents as low as 50pA.

If input voltage vi is set to zero volt,  $V_0 = 0 \, \text{V}$ .

for 741 op-amp, IMIL feed boack Revistor,

Vo = 500nA × IMIL.

= 500mV.

The output is driven to soom, with zero input due to bias consents.

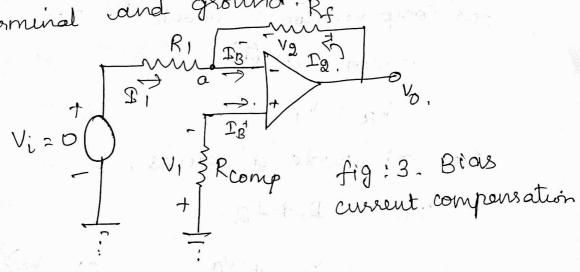

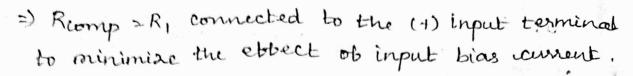

This ebbect can be compensated by using a compensation Resistor Rcomp using a compensation resistor Rcomp added in between the non inverting input condided and ground. Rf

current Ist flowing through Rcomp develops a voltage V, across it.

-Vi+0+V2-V0=0.

By proper value of Rcomp,

Va cancelled with V,.

So, Vo = 0.

The voltage at node a, is -V,.

$$\sum_{i} \frac{2V_{i}}{R_{i}}$$

$$I_{\alpha} = \frac{V_{\alpha}}{R_{\alpha}}$$

FOR Compensation vo should be zero,

KCL at node à guies,

$$D_{8} = V_{1} \left( \frac{R_{1} + R_{1}}{R_{1}R_{1}} \right)$$

Assume  $D_{8} = D_{8}$ ,

$$D_{7} = V_{1}$$

Sub eqn (1),

$$\frac{V_1}{R_{comp}} = \frac{V_1(R_1 + R_f)}{R_1R_f}$$

$$R comp = \frac{R_1 R_f}{R_1 + R_f} = R_1 || R_f$$

To compensate for bias currents, the compensating Periston Rcomp should be equal to the parallel combination ob resistors lied to the inverting terminal.

April 3211337 pais

phononing pais

ghorning pais

guttree

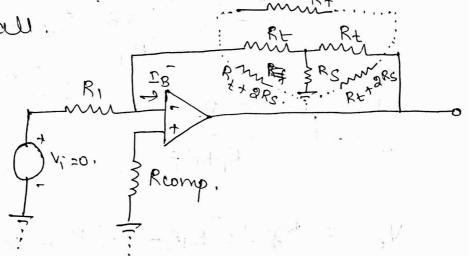

- =) Bios current compensation will work it both IB & IB are equal.

- =) But in practical, always small difference between IB' & IB. This difference is called the offset current (Los).

DOS FOR BJT op-amp is doonA.

DOS FOR FET op-amp is 10PA.

Prom fig 3,

V, = IB Rcomp.

$$\mathbb{D}_{1} = \frac{V_{1}}{R_{1}}.$$

KCL at node a gives.

$$I_1 = \frac{V_1}{R_1}$$

.

$$\begin{array}{lll} \mathbb{I}_{\mathcal{B}} &=& \mathbb{I}_{\mathcal{B}} - \left(\mathbb{I}_{\mathcal{B}}^{\dagger} & \frac{\mathsf{R}_{\mathsf{comp}}}{\mathsf{R}_{\mathsf{I}}}\right). \\ & \mathsf{Vo} &=& \mathbb{I}_{\mathcal{B}} \mathsf{R}_{\mathsf{f}} - \mathsf{V}_{\mathsf{I}}. \\ & =& \mathbb{I}_{\mathcal{B}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}}. \\ & =& \left(\mathbb{I}_{\mathcal{B}}^{\mathsf{g}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}}\right) \; \mathsf{R}_{\mathsf{f}} - \\ & =& \left(\mathbb{I}_{\mathcal{B}}^{\mathsf{g}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}}\right) \; \mathsf{R}_{\mathsf{f}} - \\ & \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} \\ & \mathsf{R}_{\mathsf{i}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{comp}} \mathsf{R}_{\mathsf{f}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} - \mathbb{I}_{\mathcal{B}}^{\dagger} \; \mathsf{R}_{\mathsf{i}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \\ & =& \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathcal{B}} \; \mathsf{R}_{\mathsf{i}} + \mathbb{I}_{\mathsf{i}} + \mathbb{I}_{\mathsf{$$

The etbect of obbset current can be minimized by keeping beedback resistance small.

=) The etbect ob obbset current can be minimized by keeping feedback resistance — muRf....

rig shows T-beedback network.

The T-network provides a beedback signal as ib the network were a single feedback resistor.

$$R_{t} < \frac{R_{t}}{2}$$

$$R_{s} = \frac{R_{t}}{R_{t}-8R_{t}}$$

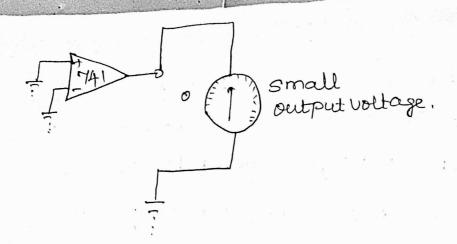

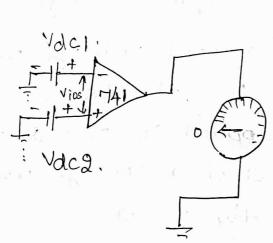

# Input offset voltage: -

- 2) whenever both the input terminals of the op-amp are grounded, the output voltage should be zero.

- 5) But ein practical, op-amp shows a small non zero output voltage.

- a small voltage in millivolts is recurred to be applied to one of the required to be applied to one of the input terminals such a voltage makes the output exactly zero.

- =) This dic voltage which makes the output voltage zero, when the other output voltage zero, when the other terminal is grounded is called input terminal is grounded by Vios.

- =) The Vios can be tre (Or) -re. Nentioned in the data sheet.

- =) Smaller the value of Vios better is the matching of the input terminals.

B - 10 - 01 - 01

le v

=) Vios depends on the temperature.

Vios = [Vac - Vaca].

output voltage is

For op-amp MAIC, the input obbset. Voltage is 6 mV.

$$Va = \left(\frac{R_1}{R_1 + R_2}\right) Vo$$

$$V_0 = \left(\frac{R_1 + R_F}{R_1}\right) V_2 = \left(1 + \frac{R_F}{R_1}\right) V_2$$

## Basic op-amp Applications:

Oscale changer/ Inverter:-

=) If the ratio  $\frac{R_5}{R_1} = k$

where k - real constant.

closed loop gain ACL = -k.

R = = R1, ACL = -1.

The circuit is could an Inverter.

The output is 180° out ob phase with respect to input.

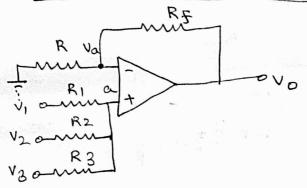

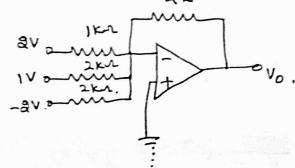

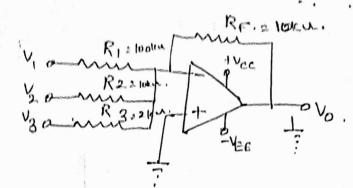

@ summing Amplifies:

2) ep-amp may be used to design a circuit whose output is the sum ab several input signals. Such a circuit is called a summing Amplities or a summer.

### Inverting summing Amplitus:

- =) A typical summing amplitude with three input input voltages V,, Vg, V3 & three input resistors R,, Ra, R3 & Feedback Perinton R, is shown in big.

- 2) For an ideal op-amp,

$AoL = \infty$ ,  $Ri = \infty$

Input bias aurent is assumed to be zero.

The voltage at node a is zero,

non-investing input terminal is grounded.

kel at node à',

$$\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{8}} + \frac{V_{0}}{R_{f}} = 0.$$

$$-\frac{V_{0}}{R_{f}} = \frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}}.$$

$$V_0 = -\left[\frac{R_F}{R_1} V_1 + \frac{R_F}{R_8} V_9 + \frac{R_F}{R_3} V_3\right].$$

The output is an inverted, Sum of the inputs,

In the special case,  $R_1 = R_2 = R_3 = R_5, \quad V_0 = -\left[V_1 + V_2 + V_3\right].$

R when, R, = Ra = R3 = 3 Rf.

$$V_0 = -\left[\frac{v_1 + v_2 + v_3}{3}\right].$$

output is the average of the input signals.

(Inverted)

ro find Rcomp, make all inputs  $V_1 = V_2 = V_3 = 0$ . Effective input resistance  $Ri = R_1 || R_2 || R_3$ .

Rcomp = Rill Rf.

Non-inverting summing Amplitus!

=> The voltage at the (-) input terminal be Va, voltage at (+) input terminal also Va.

The nodal equation at node a is given by

$$\frac{V_1}{R_1} - \frac{V_2}{R_1} + \frac{V_3}{R_2} - \frac{V_3}{R_2} - \frac{V_3}{R_3} = 0$$

$$\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{8}} + \frac{V_{3}}{R_{3}} = \frac{V_{2}}{R_{1}} + \frac{V_{2}}{R_{8}} + \frac{V_{3}}{R_{3}}.$$

$$\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}} = V_{2} \left[ \frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}} \right].$$

$$V_{0} = \frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}}$$

$$\frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}}$$

$$\frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}}$$

The op-amp & two resistors Rf, R constitute a non-inventing Amplities,

$$V_0 = \begin{bmatrix} 1 + \frac{RF}{R} \end{bmatrix} V_0.$$

$$V_0 = \frac{V_0}{1 + \frac{RF}{R}}.$$

Sub egn & in O,

$$\frac{V_0}{1+R_F} = \frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3}$$

$$\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

$$V_{0} = \begin{bmatrix} 1 + R_{\frac{1}{2}} \\ R_{1} \end{bmatrix} \begin{bmatrix} V_{1} + V_{2} + V_{3} \\ R_{1} & R_{2} \end{bmatrix} \begin{bmatrix} V_{1} + V_{2} + V_{3} \\ R_{1} & R_{2} \end{bmatrix}$$

which is a non-inverted weighted sum of inputs.

=) If all resistors are equal in value, then the output voltages can be derived wring superposition principle.

2) To find output Voi due to Vi alone,

make Va = 0. The above circuit becomes

a non-inverting amplifier, input voltage

Vi/2, at -) non-inverting terminal,

$$V_0 = \frac{V_1}{2} \left[ 1 + \frac{R}{R} \right] = V_1.$$

III by, the output vog, due to vg, alone,

Vog = -Va.

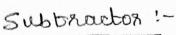

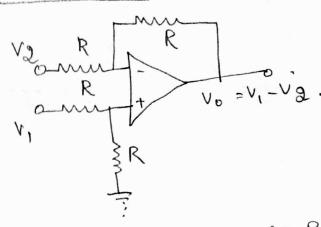

The output voltage vo due to both the inputs can be written as,

Vo = Vo1 + Voa = V, -Va.

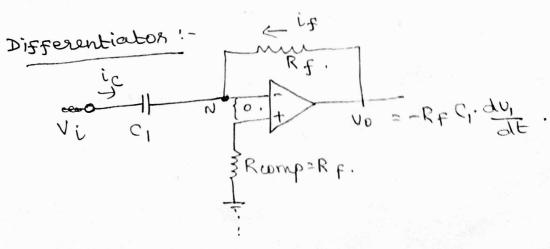

The node N is at virtual ground, VN =0, The current ic through the capacitos is. ic = C1. d [ Vi - VN]. = C1. dui The current if through beedback Resistoris Vo , Nodal equation at node N is, cercia. ic + if = 0. C, dvi + Vo = 0.  $C_{i} \frac{dv_{i}}{dt} = \frac{V_{0}}{R_{f}} \cdot \frac{V_{0}}{V_{0}} = -R_{f}C_{i} \cdot \frac{dv_{i}}{dt}$ Vo = RfC1. dx Phason equivalent 06 above equation is,  $V_0(s) = -R_f C_1 \leq V_i(s)$ vo, vi phason representations of Vo, Vi. put s = jus, |A| = | Vo | = | -jw R F C\_1 |. = WRFC1.

$$|A| = \frac{5}{5\alpha}$$

$$f_{\alpha} = \frac{1}{2\pi R_{F}C_{1}}$$

At f=fa, is1 =1, ie odB.

- 1) The gain incurred at a rate of +20d5 doods.

At high frequency, a dibberentiator.

become unstable and break into oscillations.

- a) The input impedance I we, incharces with incharce in brequency around is sensitive to high brequency noise.

Practical Differentiator:

ZI

RF

V; RI

RESPONDE = RI [RF>>R].

Transfer bunction is,  $\frac{V_0(s)}{V_1(s)} = -\frac{ZF}{ZI} = -\frac{SRF(I)}{(I+SRF(F)(I+SC_1R_1)}$

For

$$R_{f}^{c_{f}} = R_{i}^{c_{i}}$$

,

$\frac{V_{o}(s)}{V_{i}(s)} = -\frac{SR_{f}^{c_{i}}}{(1+SR_{i}^{c_{i}})^{2}} = -\frac{SR_{f}^{c_{i}}}{(1+\frac{1}{2}\frac{f}{fb})^{2}}$

fb = 1 8 TR, G, Fa< fb< fc. FOR good differentiation,

T > ReC,.

A good dibberentiator may be designed by 1) Choose to equal to the highest brighency 06 the input signal. Arrune c, < 1 MF.

a) choose  $f_b = 10fa$ calculate R, & CF.  $R_1C_1 = R_FC_F$ .

,8

1-0

13.4 %

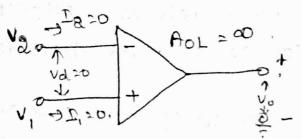

Ideal op-amp characteristics:

Fig Shows an ideal op-amp. It has a input signals V, , Va applied to noninverting and Inverting terminals.

1) An ideal op-amp draws no current at both the input terminals. i.e I, 3-820. Input impedance is intinite.

2) The gain ob an ideal op-amp is infinite (00), hence the differential. input vd = v, -va is zero for the finite output voltage vo.

# ) Infinite voltage gain: -

AOL = 00.

It is the differential open loop gain and is intinite too an ideal op-amp.

2) Indivite Input Impedance :-

Input impedance Zin = Vin

This enruses that no current can blow into an ideal op-amp.

co zero output impedanco (80=0).

The ideal op-amp acts as a perted interval vollage source with ho interval revisional

Output voltage of the op-amp remains. Same, irrespective of the value of boad revisionce connected.

d) zero obbset voltage (vios = 0).

The presence as the small output voltage though  $V_1 = V_8 = 0$  is called our observed voltage. It is zero for an ideal op-amp.

e) Intimite bound width :-

The songe ob brequency over which the ampliture perbormance is satisfactory is called its bandwidth. The bandwidth of an ideal of-amp is intinite.

The gaun of the op-amp will be constant over the brequency range from d.c (o frequency) to do frequency.

P) Intimula CMRR (p=0).

CMRR = Differential gain Common mode gain

Thus for an ideal op-amp. common mode gain is O. so, CMRR is ao.

9) Infinite slew rate: (s =00).

expressed in V/Ms.

h) no effect of temperature

i) Power rupply Rejection Ratio:

The power supply rejection ratio is defined as the ratio of the change in input offset voltage due to the change in supply voltage producing it.

Ideal value is zero.

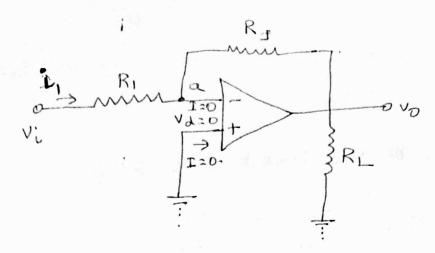

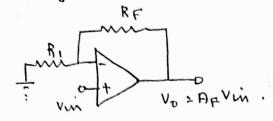

# The Inverting Amplibies

=) This circuit need of all the op-amp circuits.

=) The output voltage vo is bed back to the inverting input terminal through the R<sub>f</sub>-R<sub>1</sub> inverting input terminal through the R<sub>f</sub>-R<sub>1</sub>

## Rf & Feed borck Resiston.

2) Input signal Vi applied to the inverting input through R, , Non-inverting input terminal of op amp is grounded.

### Analyris :-

Assume an ideal op-aump. node a is at grounded potential. Current i, through R, is,

op-amps draw no current.

output vollage,

- ve sign indicales a phare shift 06 180° between vi & Vo.

gain of the inverting amplifier,

$$A_{CL} = \frac{V_0}{V_L} = -\frac{R_F}{R_I}$$

Nodal Equation at the node a' is,

Va > voltage at node a. a is at virtual ground. Va = 0.

- =) The value Ob R, kept large to avoid loading effect.

- =) Load Resistor R.L is put at the output.

- => If Revistances R, and Rf are replaced by impedances Z; B Zf, then

Foundtion (3) is valid only if the op-amp is an ideal one. For a practical, enpression for dored loop voltage gain calculated using low brequency model.

## Practical Inverting Amplitude:

The input impedance Ri ob an op-amp is mually greater than RI.

So, arrume Veg = Vi, Reg = R,

From the output loop, fig(b),

$$0 \Rightarrow \frac{V_0 - iR_0}{A_{0L}} = V_d . \qquad (3).$$

sub (3) in eqn (2),

Vo (V+

Vo-iRo+iRfAOL+VOAOL=0,

$$V_{0} = 0$$

.

$V_{0} = 0$ .

$V_{0} = 0$ .

KUL loop equation, (Ro-RSPOL)

put the value i from eqn (4) in eqn (5). out out that the the the widows

$$AcL = \frac{Vo}{Vi} = \frac{Ro - AoLR_f}{Ro + R_f + R_i (1 + AoL)}$$

AOL >>1, AOLR, >> RO+RF.

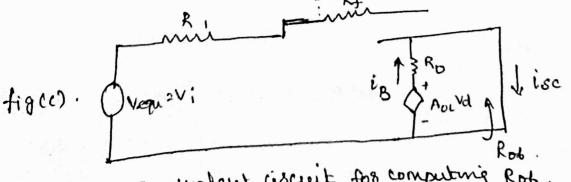

#### Input Revistance Ri

writing the loop equation and solving for Rif,

Equivalent circuit of a practical op-amp inverting Amplitier.

simplified circuit bring Thevenin's convalent.

Eouivalent circuit for computing Rob.

#### A.C characteristics.

#### Frequency Response:

Ideally an ep-amp have an intinite bandwidth. It its open loop gain is 90 dB, with d.c signal its gain should remain the same, 90 dB through audio and on to high radio frequencies. The practical op-amp gain, decreases (rolls-eff) at higher frequencies.

- =) It is because there must be a capacitive component in the equivalent circuit of the op-amp. This capacitance is due to the physical characteristics of the device (BJT OS FET) wed and internal construction of op-amp.

- =) For an ep-amp with only one break (corner)

Frequency, all the capacitor ebbects can be

represented by a single capacitor C.

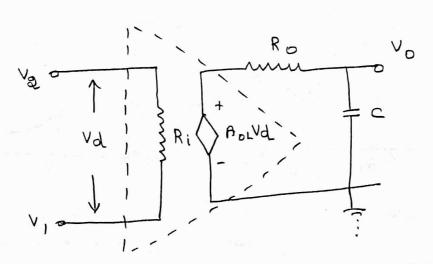

Fig: High Frequency model at an ap-amp with single corner frequency.

The open loop voltage gain ob an op-amp is  $V_0 = \frac{-\dot{J}Xc}{R_0 - \dot{J}Xc} \quad A_{0L}Vd.$

$$A = \frac{AoL}{(1715)}$$

The magnitude and the phase angle of the open we loop voltage gain is

$$|A| = \frac{AoL}{\sqrt{1+(\pm 1\pm 1)^2}}$$

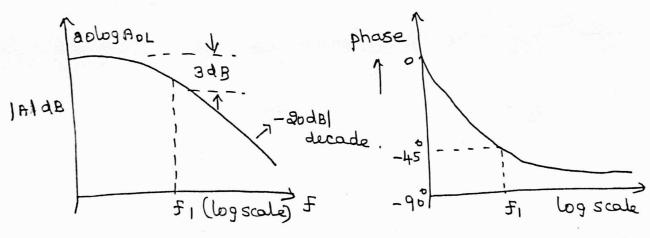

open bop magnitude characteristics in semilog paper phase characteristics for an op-amp with single break frequency.

=) From the fig, phase characteristics phase angle is zero at frequency f=0. At corner frequency  $f_1$ , the phase angle is  $-45^{\circ}$  (lagging), at intinite frequency the phase angle is  $-9^{\circ}$ .

A =

$$AoL$$

$1+i(f|f_1)$

$1+i(w|w_1)$

$AoL$

$AoL$

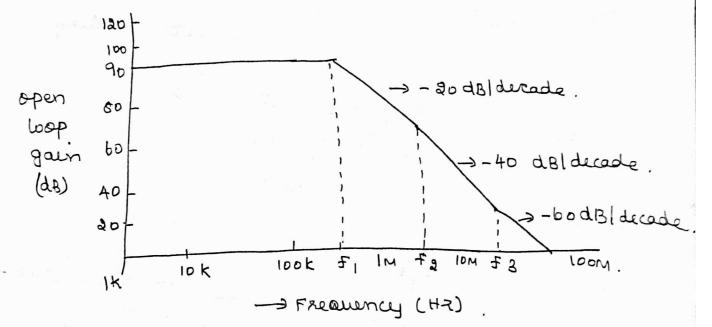

The transfer function of our op-ourse with three break frequencies can be assumed

$$A = \frac{AoL}{\left[1+\dot{d}f|_{F_1}\right]\left[1+\dot{d}f|_{F_2}\right]\left[1+\dot{d}f|_{F_2}\right]} \sim f_2.$$

$$A = \frac{A_{0}L \cdot \omega_{1} \cdot \omega_{2} \cdot \omega_{3}}{(s+\omega_{1})(s+\omega_{2})(s+\omega_{3})}.$$

0 < 60, < 602 < 603.

Approximation of open loop gain Us Fredring and, open loop fredring response is flat (90dB)

From low fredrincies to 800 kHz.

The gain drops from 90 dB to 70 dB, at 200KHZ -24HZ.

At Freemency from aMHZ - BOMHZ, rolls obs rate is -40 dBlderade.

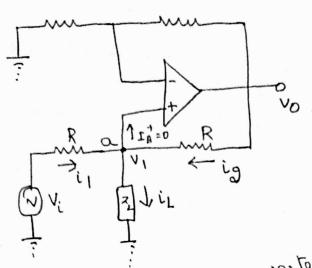

#### A fo I commerter ..

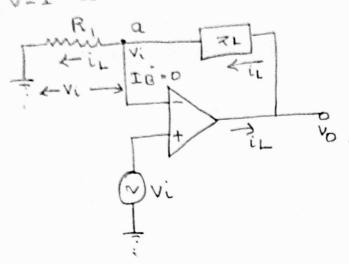

voltage to current converter :-

For many applications, one may have to convert a voltage signal to a propostional output current. For this, two types of corcuits possible,

V-I converter with floating load. V-I converter with grounded load.

voltage to current converter with floating

=) In the above big ZL is floating. voltage at node a' is vi,

Vi = i\_RI (as Ig = 0).

il = Vi

Ri\*

The input voltage vi is converted with an output current of VIRI. The same current flowing through the load and signal source.

Voltage to current converter with grounded load.

Let VI be the voltage at node a,

using KUL,

$$\frac{V_i - V_j}{R} + \frac{V_0 - V_j}{R} = L$$

Vi + Vo - & VI = iLR.

$$V_1 = \frac{V_1 + V_0 - iLR}{2}$$

op-amp is non-inverting mode, the gain ob the circuit is  $1 + R|_{R} = 2$ . The output voltage is,

A voltage to current converter is used for low voltage dc and ac voltmeter, LED, zener diode tester.

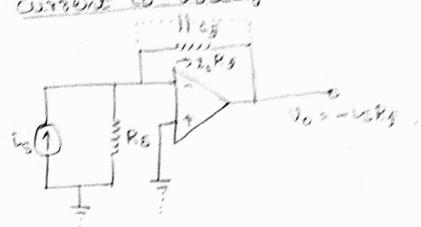

CONTROLL TO VOLLAGE CONTRACTOR

- a) Photocell, photodicale, photosopholic all give an encount output arrent that is proportional to an incident radiant energy on light.

- to voltage viving a = V + V (involver).

- E)(-) input berminal is at virtual ground, no current thous through Rs and virtual ground, no through the feed back Resistor Rs.

Thous through the feed back Resistor Rs.

Output voltage  $V_0 = -i \leq Rs$ .

- =) MATHI (IB = 3NA) used to detect lower currents.

- E) Risistor Rf shunted with a capacitor

Cf to reduce high frequency noise and

possibility of oscillations.

50

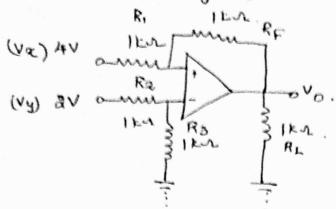

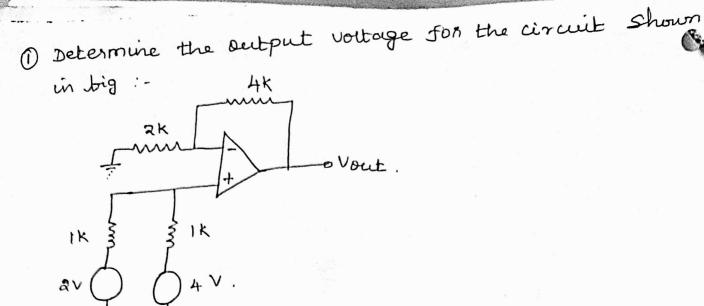

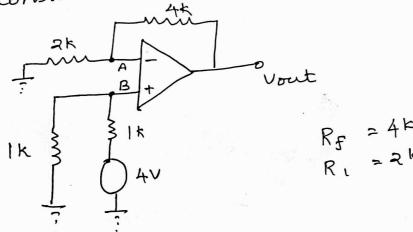

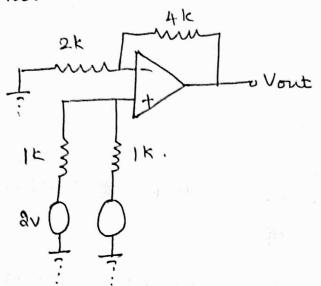

For the circuit diagram shown below determine the output voltage Vo:

Solution: -

$$V_0 = -\frac{R_F}{R_I} \left( V_x - V_y \right).$$

$$= -\frac{1 \text{ kel}}{1 \text{ kel}} \left( A - A \right).$$

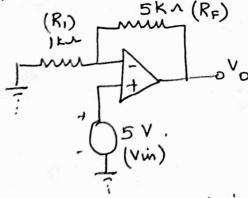

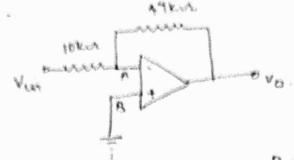

For the non-inverting Amplifier,

$$\frac{V_0}{V_{\text{UM}}} = 1 + \frac{R_E}{R_1}.$$

$$= 1 + \frac{5}{1}$$

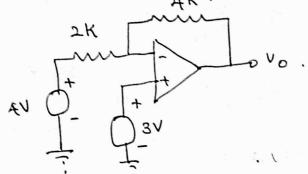

(ii) Determine the output voltage for the given circuit: 2k

This is an investing summing Amplifier.

$$V_{0} = -\left[\frac{R_{F}}{R_{I}}V_{I} + \frac{R_{F}}{R_{D}}V_{Q} + \frac{R_{F}}{R_{D}}V_{3}\right].$$

$$= -\left[\frac{2KL(2) + \frac{2}{Q}}{1KL}(1) + \frac{2}{Q}(-2)\right].$$

$$= -\left[4 + 1 - 2\right].$$

1 Determine the vollage gain of the op. amp Shown in July : -

Given: R, aloku, RF = 47km.

The circuit is inventing Amplifier

Grain =

$$\frac{V_0}{V_{UN}} = -\frac{R_{Pl}}{R_1} = \frac{47 \times 10^3}{10 \times 10^3} = -4.7$$

-ve sign indicates phase shift he investing mode.

(8) An input ob 30 is sed to the non-inverting teaminal to an operational Amplifus. The amplibus has Ricolokul, RF =10 KM, Find the subput voltage

R1 = 10KM, RF = 10KM, Vin = 3V.

$$AF = \frac{1+10}{10} = \frac{2}{3}$$

$$AF = \frac{V_0}{V_m} = \frac{2}{3}$$

$$V_0 = \frac{5}{3}$$

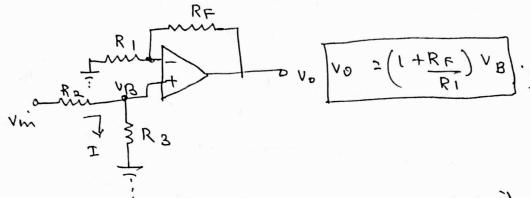

Key pount: - Non inverting Amplifier always amplifies voltage at its non-inverting terminal.

Vin directly applied.

Vin applied through resistive around

$$V_{B} = \frac{R_{3}}{R_{3} + R_{3}} \times V_{in}.$$

$$V_{D} = \frac{1 + R_{F}}{R_{1}} \frac{R_{3}}{R_{2} + R_{3}} \times V_{in}.$$

8 Find to for the circuit shown below: -

$$V_0 = \left(1 + \frac{R_F}{R_I}\right) V_B.$$

$$= 1 \left[\frac{50 \times 10^3}{10 \times 10^3}\right] 5$$

Find Vo for the following circuit ! -

when to is acting, 30 is grounded, then it is investing amplifier.

$$= -\left(\frac{4}{2}\right) \times 4 = -8 \text{ V}.$$

when 3V is acting, 4V is grounded, it is non-involved. non-inverting amplifier

Vog =

$$\left(1 + \frac{RF}{RI}\right) \times 3 = \left(1 + \frac{4}{2}\right) \times 3$$

.

when 3v is acting, 4v is grownded. Le acts on non-viewerting amplifies.

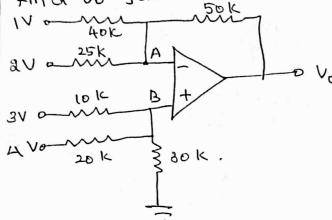

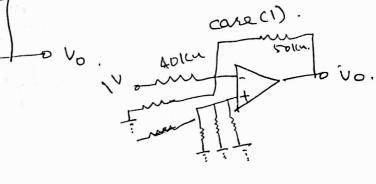

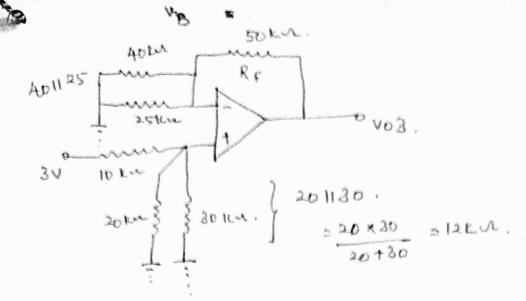

5) Find Vo For the following circuit: -

case! Iv is acting, all the sources grounded.

Node B is grounded, node A is virtual ground.

25 km does not covery any current.

Voi = RF) Vin (Inverting).

$$=-\left(\frac{50}{40}\right)\times 1$$

= -1.25 V.

case à 2 v is acting, all the sources are ground

Vog =

$$-\left(\frac{50}{85}\right) \times 2 = -40$$

. (Irwesting).

cared .

3 v is acting, all the sources are grounded.

Ret

$$\sim V_B = \left(\frac{R_3}{R_2 + R_3}\right) v_{in}$$

.

=15.3846KM

$$V_B = \frac{R_2}{(R_2 + R_3)} \times 3$$

.

$$= \frac{18}{(10 + 12)} \times 3$$

.

= 1.6363 V.

= 6.9545V.

$$V_{0} = \frac{7.5}{15.3846}$$

$$V_{0} = \frac{7.5}{15.3846}$$

$$V_{0} = \frac{7.5}{15.3846}$$

$$V_{0} = \frac{1.0909}{15.3846}$$

Vo = Vo1 + Vo2 + Vo3 + Vo4 . = 4.6363 V . = -1.85 - 4 + 6.9545 + 4.6363 -= 6.3408 V .

solution: - use superposition principle. consider 4V alone, short QV.

$V_B = \frac{1 \text{ kn}}{(1 \text{ kn} + 1 \text{ kn})} \times 4V$ . [use potential duider rule].

Vol = [1 + Rf RI] VB.

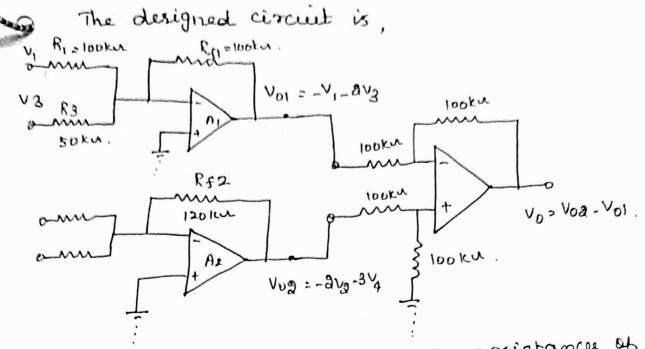

1 Design a op-amp circuit to give an output Vo = V1 - 2 V2 + 2 V3 - 3 V4.

The tre & -ve berns can be added separately wring two adders and then subtractor wied.

choose RF1 = 100km; FOR VI + avg.

$$V_{01} = -\left[\begin{array}{c} R_{5} \\ R_{1} \end{array} V_{1} + \frac{R_{5}}{R_{3}} V_{3} \right].$$

100ku2 R1; 100 = R3 => R3 = 501cu.

$$R_1 : \frac{100}{8}$$

$R_1 : \frac{100}{8} = -V_1 - 8V_3$

$R_1 : \frac{100}{8} = -V_1 - 8V_3$

FOR -2 V2 - 3 V4, choose Rfa = 12 blcm.

$$V_{02} = -\left[\frac{R_F}{R_2}V_2 - \frac{R_F}{R_4}V_4\right],$$

$$\frac{RF}{RQ} = 2 ; \frac{RF}{R4} = -3.$$

$$\frac{R2}{120} = R2$$

;  $\frac{120}{3} = R4$ .

$$\frac{20}{2}$$

= Ra;  $\frac{120}{3}$  =  $\frac{120}$  =  $\frac{120}{3}$  =  $\frac{120}{3}$  =  $\frac{120}{3}$  =  $\frac{120}{3}$  =

The output of subtractor is Vo = Vo2 - Vo1.

$\frac{V_0 = (-2V_2 - 3V_4) - (-V_1 - 2V_3)}{V_0 = V_1 - 2V_2 + 2V_3 - 3V_4}$

$$\frac{V_0}{V_0} = \frac{V_1 - 2V_2 + 2V_3 - 3V_4}{V_0}$$

Now consider 8V source, Short 4V.

$$V_{B} = \frac{1 \text{kn}}{1 \text{kn} + 1 \text{kn}} \times 8V.$$

$$= \frac{8}{9} = 1V.$$

$$V_{O} = \left(1 + \frac{R_{F}}{R_{1}}\right) V_{B} = \left(1 + \frac{4}{2}\right) \times 1.$$

$$= 3V.$$

Vout = Voi + Vo2 = 60+30 = 90.

1 Draw an adder circuit for the given empression Vo = - (0.14 + v2 + 5 v3).

$$V_0 = -(0.1V_1 + V_2 + 5V_3).$$

$$= -\left[\frac{R_F}{R_1}V_1 + \frac{R_F}{R_2}V_2 + \frac{R_F}{R_3}V_3\right].$$

choose RF = 10km,

hoose

$$RF = RF V_1$$

.

$$\frac{RF}{RI} = 0.1; \frac{RF}{R2} = 1; \frac{RF}{R3} = 5.$$

$$\frac{10}{0.1} = R_1$$

;  $\frac{10}{1} = R_2$ ;  $\frac{10}{5} = R_3$ .

$\frac{10}{0.1} = R_1$ ;  $\frac{10}{1} = R_2$ ;  $\frac{10}{5} = R_3$ .

$R_1 = 100 \text{ ku}$ ,  $R_2 = 10 \text{ ku}$ ,  $R_3 = 4 \text{ ku}$ .

use the subtractor with all the resistances of some value  $R = 100 \, \text{km}$ .

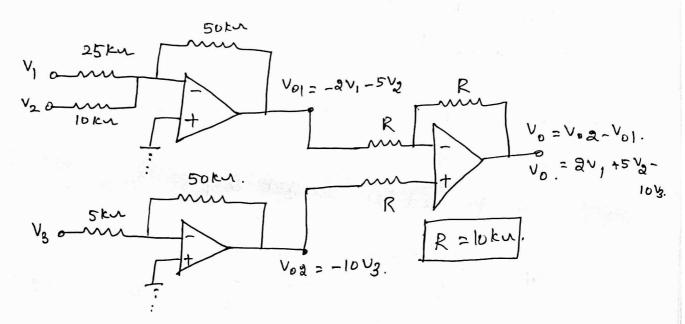

① Design an adder\_subtractor circuit for  $V_0 = 8V_1 + 5V_2 - 10V_3$ .

Step Design adder to get 24,+5 va.

$$V_{01} = -\left[\frac{RF_{1}}{R_{1}}V_{1} + \frac{RF_{1}}{Ra}V_{2}\right]^{2}$$

$\frac{RF_{1}}{R_{1}} = a$ ;  $\frac{RF_{1}}{Ra} = 5$ .  $V_{01} = -aV_{1} + 5V_{2}$ .

$\frac{RF_{1}}{Ra} = a$ ;  $\frac{RF_{1}}{Ra} = 5$ .  $V_{01} = -aV_{1} + 5V_{2}$ .

Choose  $RF_{1} = 50$ ku,  $S_{0} = 5$   $R_{1} = asku$ .

$\frac{50}{R^{2}} = 5$   $R_{2} = 10$ ku.

Generate 1013 wing investing Amplifies,

$$\frac{R_{F33}}{R_3} = 10$$

=)  $R_{F30} = 10R_3$ .

$SOR_{F3} = 50kA$ ,  $R_3 = 51kA$ .

use subtractor Vo = Voz-Vol.

$$V_0 = -10V_3 - [-2V_1 - 5V_2].$$

$$= 2V_1 + 5V_2 - 10V_3.$$

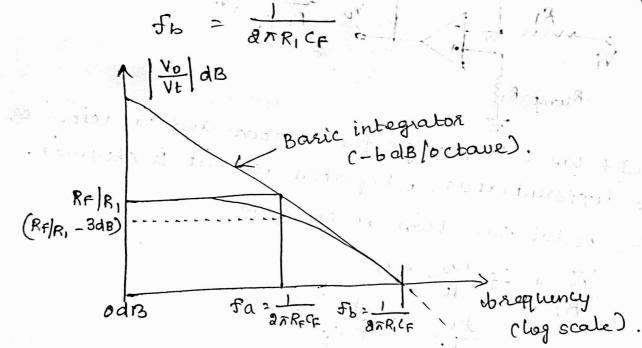

B Derign a practical Integrator circuit with a d.c. gain ob 10, to integrate a square wave of 10kHz.

dic gain for the practical Integrator,

The magnitude of the gain A is,

$$|A| = \frac{R + |R|}{\sqrt{1 + \left(\frac{f}{fa}\right)^2}}; \text{ at } f = 0, \text{ d.c. comodition}$$

$$|A| = \frac{R + |R|}{\sqrt{1 + \left(\frac{f}{fa}\right)^2}}; \text{ at } f = 0, \text{ d.c. comodition}$$

1

The input frequency of = 10kHz.

FOR proper inbegration, of ≥ 10 fa.

Ja > Break Frequency of the practical Integrator.

$$\frac{f}{fa} = 10$$

.

$fa = \frac{f}{10} = \frac{10 \times 10^{3}}{10} = 1000 Hz$ .

$fa = \frac{1}{4 \times R_{F} C_{F}}$

$fa = \frac{1}{4 \times R_{F} C_{F}}$

Choose, R, = loku, RF = 10xR, = 10x10=100ku.

$$C_F = \frac{1}{8\pi R_F \times 1000}$$

$$\frac{1}{8\pi \times 1000 \times 100 \times 10}$$

$$C_F = 1.5915 \times 10^9 (0.8) 1.6 hF.$$

Rcomp'= R, 11 RF.

Recomp =

$$\frac{10 \times 100}{10 + 100}$$

=  $9.09 \text{ km}$ .

Recomp =  $\frac{10 \times 100}{10 + 100}$  =  $9.09 \text{ km}$ .

Recomp =  $\frac{10 \times 100}{10 + 100}$  =  $\frac{9.09 \text{ km}}{10 + 100}$ .

Obesign a practical differentiator circuit that will differentiate on input signal with the finax = 100 Hz.

selm

$$R_{1}C_{1} = R_{F}C_{F}$$

;

$$C_{F} = \frac{1.591}{R_{F}} \times \frac{0.01M_{F}}{R_{F}}$$

$$C_{F} = \frac{R_{F}C_{F}}{R_{F}} = \frac{1.591}{15.91} \times \frac{0.01M_{F}}{10.01M_{F}}$$

steps to derign practical Differentiation!

O choose fa ou the highest proquency of the input signal.

D'choose c, leu than IMF, calculate Rp.

(3) choose of as 10 times of a which ensures Dealculate Ry, Cp, brom Ric, = RFCP.

B Rcomp = RITIRE. Practically earned to RI.

Integrator :- CF Riomp-Ris

2) If we interchange the registor and capacitor of the differentiator, integrator circuit is obtained.

The nodal equation at Node N

$$\frac{V_i^2 + C_f \frac{dV_0}{dt}}{R_1} = 0$$

$$\frac{dV_0}{dt} = -\frac{1}{R_1 C_f} V_i^2$$

Integrating both sides we get.

Volo) - initial output voltage.

=) o/p voltage propositional to the time integral of the input, RICF & time constant of the integrator.

$$V_0(s) = -\frac{1}{sR_1C_F}V_1(s)$$

.

$s = j\omega$ ,

$V_0(j\omega) = -\frac{1}{j\omega R_1C_F}V_1(j\omega)$ .

The frequency of b is the brequency at which the gain of the integrator is odB and is given by;

Enguency response of a basic and Lossy integrator.

of delivery on forders to ( out

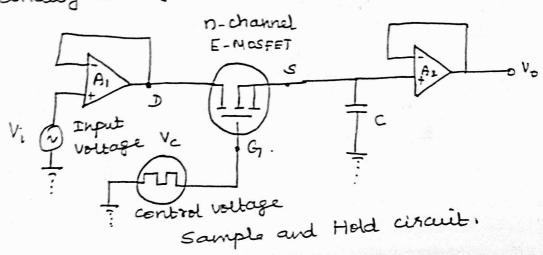

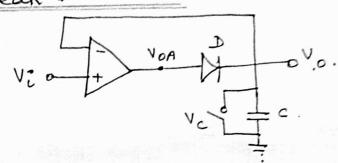

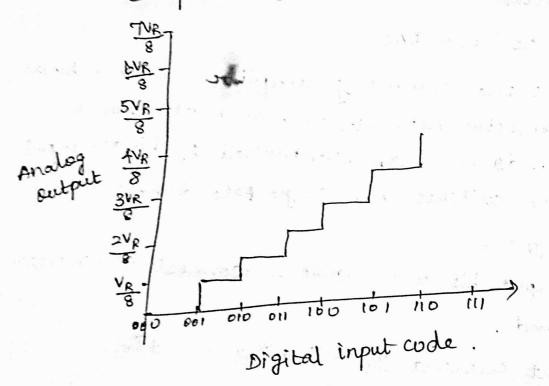

#### Applications of op-amp.

Instrumentation Amplitus and its applications

The transducer Bridge, Log and Antilog Amplifiers,

Analog multiplier & Divider, First and second order

active filters, Comparators, multivibrators, waveform

generators, clippers, clampers, Peak detector,

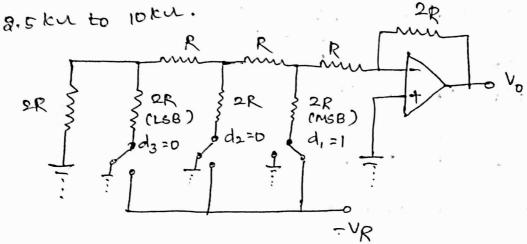

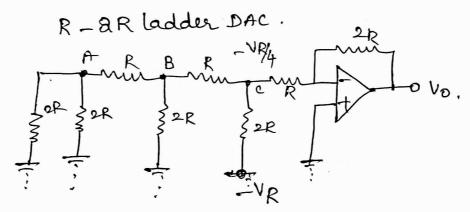

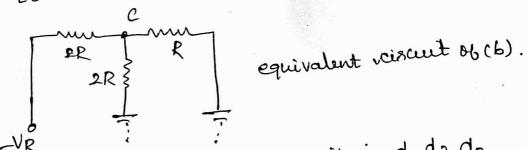

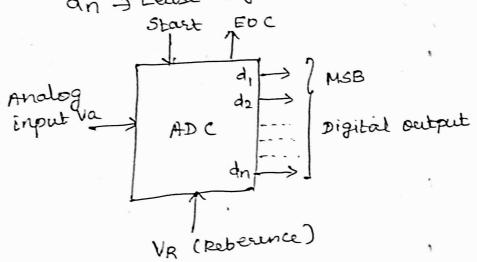

s/H circuit, D/A Converter (R-AR ladder and

weighted resistor types), A/D converters using

op-amps.

# Instrumentation Amplifiers:-

The special amplifier which is used for such a low level amplification with high cMRR, high input impedance to avoid lading, low power consumption and some other features is called an Instrumentation Amplifier.

It is also called data amplifier and is barically a difference Amplifier.

The expression for voltage 8 aun is,

V<sub>0</sub> → output of the Amplifier.

Va-V, → Differential input which is to be amp red.

Requirements of a Good Drobrumentation Amplifus

#### 1) Finite, accurate and stable gain: -

As very low level signals are required to be amplified by the Instrumentation Amplifiers. The gain in the range of 1 to 1000. The gain has to be accurate and closed loop gain must be stable.

#### 3) Easier gain adjustment:

The gain adjustment must be easier and precise. Gain adjustment is done wing a Potentiometer or digitally with the help of switches which are JFET or MOSFET switches.

#### 3) High input impedance:

To avoid the loading of input sources, input impedance of the instrumentation Amplifier must be very high.

#### 4) Low output impedance:-

Externally low output impedance (ideally zero) to avoid the loading.

- 5) High CMRR.

- 6) Low power consumption.

- 7) Low thermal and time drifts.

- 8) High slew rate.

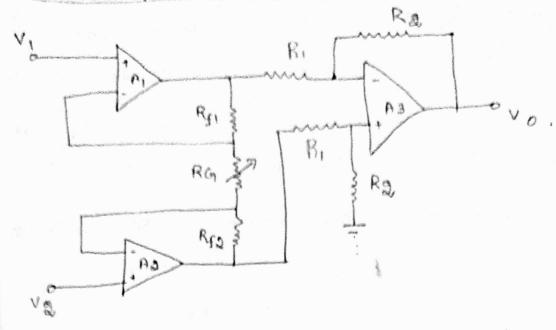

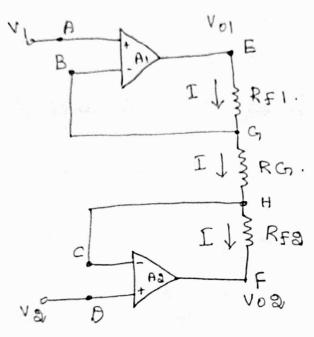

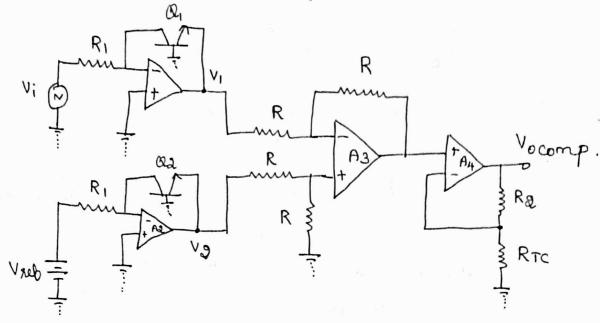

# Three op-amp Instrumentation Amplifica :-

Analysis of Three op-amp Enstrumentation Amplifier:

The output of the op-amp Aa is voa.

The node A potential of op-amp A, is VI.

Realistic Assumption, the potential of node B

is also VI. Potential of G is also VI.

The node D potential ab ep-amp Aa is va. I From the realistic assumption, potential of node c is also va. Potential ab H is also va

2) Input current at ap-amp A, Aa both are o I remains same through RFIRGRFA.

Apply ohm's law between nodes E and F,

Let R f1 = R f2 = R f.

$$\frac{1}{8R_{5}+R_{5}} = \frac{V_{01}-V_{02}}{8R_{5}+R_{5}}$$

observation of nodes G and H,

$$\frac{1}{RG} = \frac{V_G - V_H}{RG} = \frac{V_I - V_R}{RG} = \frac{C3}{RG}$$

Equate (8) & (3),

$$V_{02} - V_{01} = \frac{(8R_{f} + R_{G})(V_{2} - V_{1})'}{R_{G}} - (4)$$

sub

$$\bigcirc$$

in  $\bigcirc$ ,

overall

gain ob

the circuit  $V_0 = \frac{Ra}{R_1} \left[ \frac{(2R_F + RG)(Va - V_1)}{RG} \right]$

example  $V_0 = \frac{Ra}{R_1} \left[ \frac{1 + \frac{2R_F}{RG}}{RG} \left[ \frac{Va - V_1}{RG} \right] \right]$

#### Advantages :-

- 1) Due to variable resistance RG, the gain can be easily varied.

- a) The input impedance depends on the input impedance of non-inverting amplifur's which is high.

- 3) The output impedance of the op-amp A3 which is very very love.

- 4) The CMRR of the op-amp A3 is very high.

### Applications!

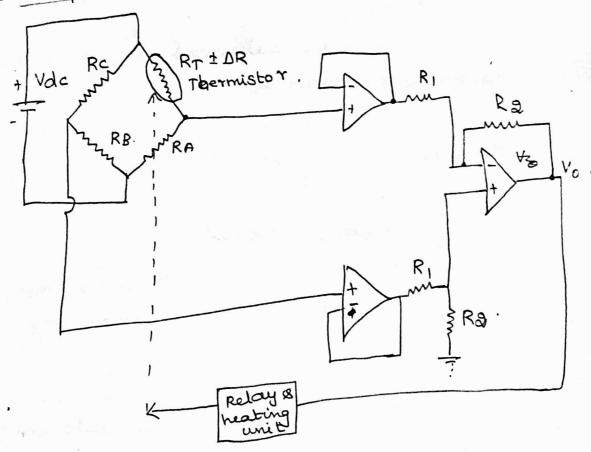

# (1) remperature controller:

simple temperature controller.

- constructed using thermistor in the transducer bridge.

- >) The bridge is set balanced for a particular reberrence temperature.

- =) Any change in this temperature, the instrumen.

- -bation amplifier produces the output voltage.

- which inturn controls the on-off of the heating unit to control temperature.

- (8) Temperature Indicator:-

- =) The same circuit used as temperature indicator.

- => Bridge is kept balanced at some reberence temperature when Vo = 0 V.

- => The meter connected at the output is calibrated. As temp changes, amplifies output also changes.

- (3) light intensity Meter: -

- =) In the same ciscuit thermistor replaced with a photocell used as a simple light intensity meter.

- => The bridge is made balanced for the darkness condition. When Light falls on the photocell its resistance changes and produces unbalanced bridge condition.

- => This produces the output, which inturn produces the meter detlection.

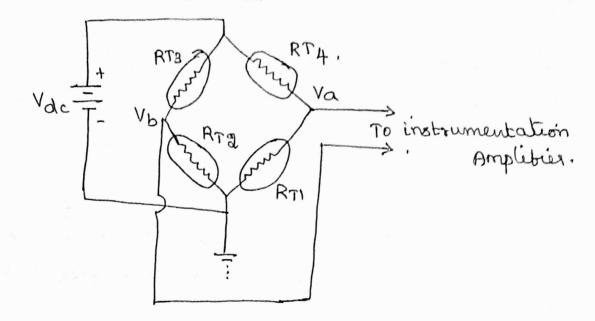

# Analog weight scale :-

- =) strain gauges are used in all the four arms of the bridge can be used as a simple analog weight scale.

- =) The elements are mounted on the borne of the weight platform.

stroum gauges in the opposite arm clongabe while the stroum gauges in other two opposite arms get com pressed.

RTI, RT3 decreases. RT3, RT4 increases.

under no weight on the platform, the bridge is

balanced RTI = RT2 = RT3 = RT4 = R. Bridge output

is ov.

unbalanced Condition, the change in Resistance is AR ohms. Increase of DR for RTD, RTH, Decrease of DR for RTI, RT3.

$$V_{b} = \frac{(R + \Delta R) V dC}{R - \Delta R + R + \Delta R} = \frac{(R + \Delta R) V dC}{2R}$$

$$V_{a} = \frac{(R - \Delta R) V dC}{(R - \Delta R) V dC} = \frac{(R - \Delta R) V dC}{2R}$$

$$V_{ab} = V_{b} - V_{a} = \frac{(R + \Delta R) V dC}{2R} = \frac{(R - \Delta R) V dC}{2R}$$

Net output voltage is,

#### Log and Antilog Amplifier: -

- 2) To have direct dB display on digital voltmeter and Spectrum analyses, Log amplifier wed to Perborn this bunctum.

- 2) Log amplifier wed to compress the dynamic range of a signal.

Fundamental log Amp circuit.

- =) A grounded base transistor is placed in the feedback path. Collector is held at virtual ground and the base is also grounded.

- => The Eransistor's voltage-current relationship becomes that ab a diode.

Ic = IE box a grounded borne Transistor.

Ic = Is [e qVE | KT - ].

where Is = Emitter Saturation current = 10 A.

A = Boltzmann's Constant

T = Absolute temperature (m°k).

Taking natural log on both sides,

$$T_C = \frac{Vi}{R_1}$$

$$-V_0 = \frac{kT}{q} ln \left[ \frac{V_i}{R_i Is} \right].$$

$$V_0 = -kT \ln \left[ \frac{V_i}{V_{reb}} \right]$$

.

where Vreb = R, Is

2) The emitter saturation current Is varies from transistor to transistor and with temperature So, stable reberence voltage Vreb cannot be obtain

This is eliminated by the circuit

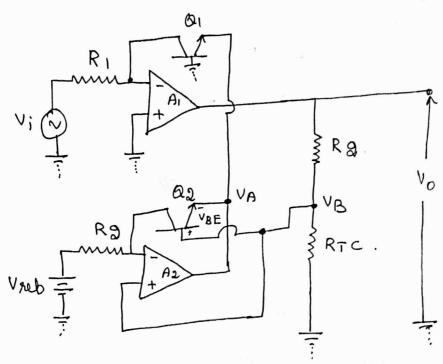

Log amplifier with saturation current and temperature compensation.

Assume,

$$I_{SI} = I_{SQ} = I_{S}$$

.

$$V_{I} = -\frac{kT}{Q} \ln \left( \frac{V_{I}}{R_{I}I_{S}} \right).$$

$$V_{Q} = -\frac{kT}{Q} \ln \left( \frac{V_{RD}}{R_{I}I_{S}} \right).$$

$$V_{Q} = V_{Q} - V_{I} = -\frac{kT}{Q} \ln \left( \frac{V_{RD}}{R_{I}I_{S}} \right) - \frac{kT}{Q} \ln \left( \frac{V_{I}}{R_{I}I_{S}} \right).$$

$$= \frac{kT}{Q} \left[ -\ln \left( \frac{V_{RD}}{R_{I}I_{S}} \right) + \ln \left( \frac{V_{I}}{R_{I}I_{S}} \right) \right].$$

$$= \frac{kT}{Q} \left[ \ln \left( \frac{V_{I}}{R_{I}I_{S}} \right) - \ln \left[ \frac{V_{RD}}{R_{I}I_{S}} \right].$$

$$V_{Q} = \frac{kT}{Q} \left[ \ln \frac{V_{I}}{R_{I}I_{S}} \right] = \frac{kT}{Q} \left[ \ln \frac{V_{I}}{V_{RD}} \right].$$

Reberence level viet is now set. dependent upon temperature and directly Proportional to T. The ap-amp A4 provides a non-inventing gain of 1+ Re

=) The circuit is expensive, reduces 4 op-amps. The same circuit obtained wing two op. amps.

log amplitier wring two-op-amps only.

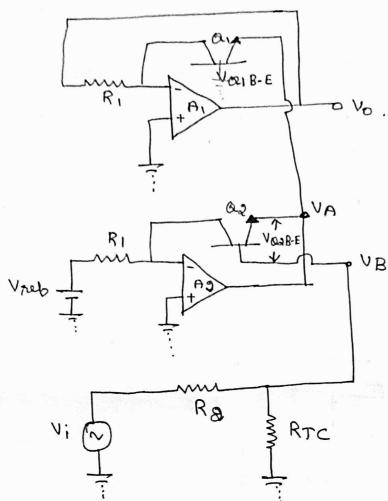

Antilog Amplitier: -

=) The input Vi for the antilog-amp is fed into the temperature compensating voltage divider R& and RTC and then to the base 06 Qg. =) The output Vo of the antilog amp is bed back to the inverting input of A, through Peris ton R,.

Since the base of Q, is tied to ground,

Antilog Amplitier.

The bare voltage VB 00 Qa is,

The voltage at the emitter of Qa is,

Emitter voltage of ag is VA,

Terespo

$$\frac{RTC}{Ra + RTC} V_{c}^{2} = -\frac{RT}{9} \left[ \ln \frac{V_{c}}{R_{s} \pm S} - \ln \frac{V \pm b}{R_{s} \pm S} \right]$$

$$-\frac{9}{KT} \times \frac{RTC}{Ra + RTC} V_{c}^{0} = \ln \left[ \frac{V_{c}}{V_{A} \pm b} \right]$$

changing natural log change in to leg 10.

$$-0.4343 \left(\frac{q}{RT}\right) \left(\frac{RTC}{Ra+RTC}\right) v_1^2 = 0.4343 \times ln\left(\frac{v_c}{v_{Ra}}\right)$$

$$-k^{l}v_1^2 = log_{10}\left(\frac{v_c}{v_{Rab}}\right)$$

where  $k^{l} = 0.4343 \left(\frac{q}{KT}\right) \left(\frac{RTC}{Ra+RTC}\right)$ .

$$-k^{l}v_1^2 = \frac{V_0}{V_{Rab}}$$

$$V_0 = V_{Rab} \left(10\right)$$

755 log/antilez amplitur Ic chip is available.

Analog Multiplier: .

Applications :-

(i) Frequency doubling.

cii) Measurement of real power.

iii) Detecting phare-angle difference between two signals at equal breamency.

(iv) Multiplying two signals

V) Dividing one signal by another.

Vi) Talking sauare root of a signal

vii) Sauaring a signal.

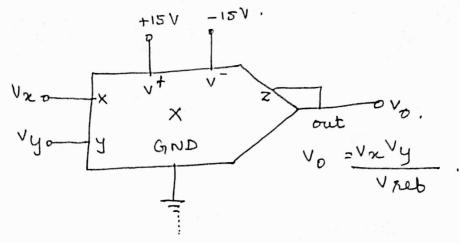

Multiplier Symbol.

Two signal inputs (Ux, Vy) are provided.

The output is the product of the two inputs

divided by a reberence voltage Vreb.

Internally vieb is set to lovalt.

As long as,

Vx < Vreb.

Power Supply voltage can range From ±8V to ±18V. whally power supplies wed for ±15V.

- =) Both inputs are positive, Ic -> one auadrant multiplier =) one input is the, the other is allowed to swing both the 8-re, -> Two auadrant multiplier.

- =) If both inputs either +ve or -ve, Ic -> Four audrant multiplier.

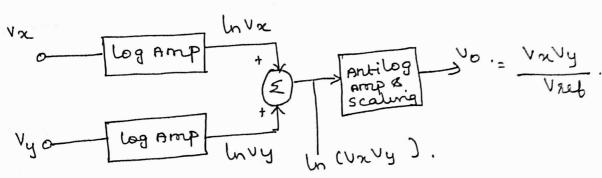

Log-antilog method: -

lnvx+lnvy=ln(vxvy).

sum of the logarithm of two numbers equals the logarithms of the product of those numbers.

multiplier Ic chips are AD 533, AD 534, AD 633.

## Frequency Doubling ! -

Let Vm = Vn Sin wt

Vy = Vy sin (wt+0).

0 -> phase difference between two signals

Vo = Voc Vy sinut (sinut cosa + sina coswt).

Vreb (sin wt cosa + Sin a sin wt cosuz)

sing = 1- cos a. - c1)

cos 2 = 2 cos 2 - 1. - c2)

0058/24 = 1 cos8x + 1. cos8x = 1+ cos8x = cos8x + 121) cos8x = 1 + 1 cos8x.

sinda =

$$1 - \frac{1}{2} - (\frac{1}{2}) \cos 8a$$

.

=  $\frac{1}{3} - \frac{1}{3} \cos 8a$ .

$\frac{1}{3} - \frac{1}{3} \cos 8a$ .

The circuit works as an ideal doubler, it same frequency is applied to both the inputs.

The output contours a de term and a regative cosine wowe ob double brequency. It is removed by using a IMF coupling capacitor between load and the output terminal.

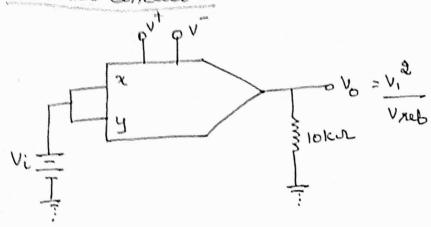

Sanarer arail :-

#### sauarer circuit

Baric multiplier can be used to saware any the or we number. The number represented by a voltage between 0 to Vzeb.

- =) Vi representing the number is connected to both the inputs.

- =) It is possible to sauare a sinewave voltage too.

- =) scriewave voltage Vi = Vm sinut is applied to both the inputs.

$$V_0 = \frac{V_1^2}{V_{Reb}}$$

$V_1 = 5 \sin 4 \pi \times 10^4 E$

$V_{Reb} = 10 V$

$V_{Neb} = 1$

The output contains de term and Frequency is doubled.

Phase angle Detection:

The two input signals applied to a multiplier are

The phase difference a between the two input signals can be calculated From the dc Component in the output voltage Vo.

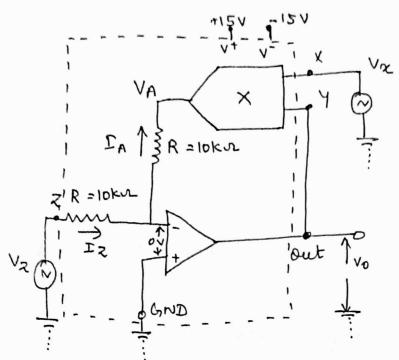

#### Divider :-

Diviruin, the complement of multiplication can be accomplished by placing the multiplier circuit in the op-amp's beedback loop.

Input signals 12 & to 12 as dividend and divisor respectively.

The op-amp's inverting terminal is at virtual ground.

$$\begin{aligned}

\mathbf{I}_{\mathcal{Z}} &= \mathbf{I}_{\mathcal{A}} \\

\mathbf{I}_{\mathcal{Z}} &= \frac{V_{\mathcal{Z}}}{R} \\

V_{\mathcal{A}} &= \frac{V_{\mathcal{Z}} V_{\mathcal{Y}}}{V_{\mathcal{R}} b} &= \frac{V_{\mathcal{Z}} V_{\mathcal{O}}}{V_{\mathcal{R}} b} \\

V_{\mathcal{A}} &= -\mathbf{I}_{\mathcal{A}} R.

\end{aligned}$$

Multiplier Ic Contigued as divider.

$$I_{\mathcal{Z}} = I_{\mathcal{A}}$$

$$I_{\mathcal{Z}} = -\frac{V_{\mathcal{X}}V_{\mathcal{O}}}{V_{\text{Reb}}R}$$

$$V_{\mathcal{Z}} = I_{\mathcal{Z}}R = -\frac{V_{\mathcal{X}}V_{\mathcal{O}}}{V_{\text{Reb}}R} \times R = -\frac{V_{\mathcal{X}}V_{\mathcal{O}}}{V_{\text{Reb}}}$$

$$V_{\mathcal{O}} = -\frac{V_{\mathcal{X}}V_{\mathcal{O}}}{V_{\mathcal{X}}}$$

To find Square Roots: -

A divider circuit wed to find soware roots by connecting both the inputs of the multiplier to the output ob an op-amp.

VA =

$$\frac{V_0}{V_{reb}}$$

$V_A = -V_{in}$

$V_0^2 = -V_{in} \cdot V_{reb} \cdot V_{o} = \sqrt{V_{reb} \cdot |V_{in}|}$

$V_0 = \sqrt{V_{reb} \cdot |V_{in}|}$

output to is proportional to square root of magnitude of Vin. Vin range between -1 15 - 10 V.

Finding Saware roots.

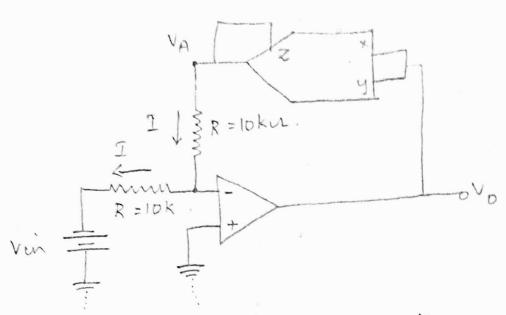

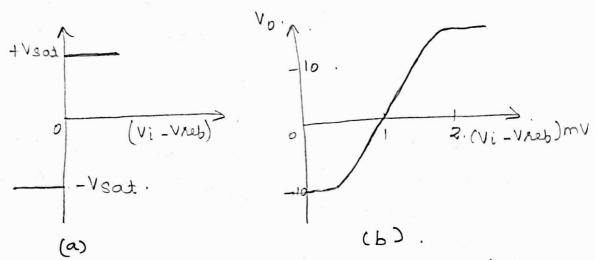

comparators: -

A comparator is a circuit which compares a signal voltage applied at one input of an op-amp with a known reberence voltage at the other output.

Transfer characteristics (a) Ideal comparator (b) practical comparator.

30

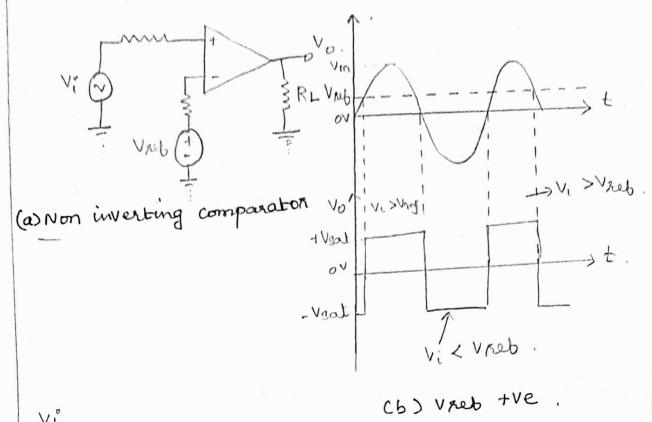

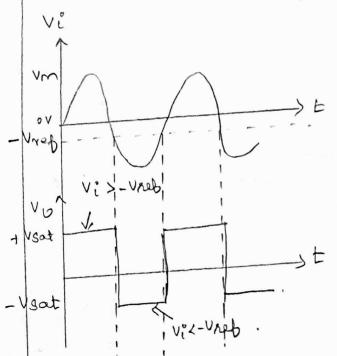

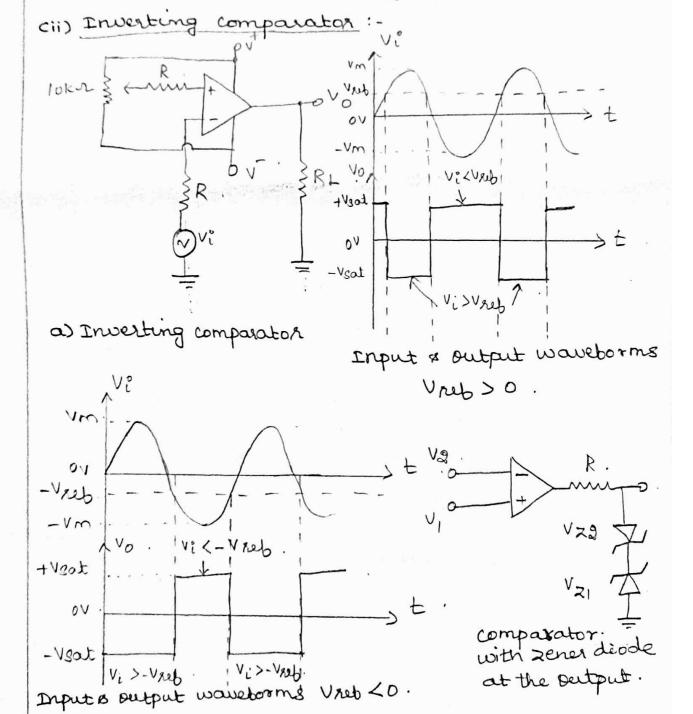

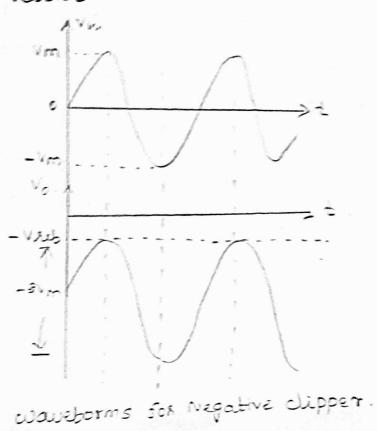

clavilification ob comparators is Non-inverting comparator. ii) Inverting comparator.

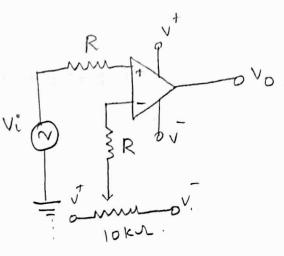

# ci) Non-inverting comparator:

(d) practical Non-inverting comparator

and a time varying signal vi is applied to (+) input.

The subjut vortage is at -Vsat for Vi > Vreb.

The subjut vortage is at +Vsat for Vi > Vreb.

s) The output waveborn is a sinusoidal input signal applied to the (+) input.

=> In a practical circuit, viet is obtained by using a loker potentiometer which forms a voltage divider with the supply voltages vt & v. Vreb abtained by adjusting the loker potentiometer.

Fix a practical inverting comparator, reberence voltage is applied to the (+) input and Vi is applied to (-) imput.

#### Applications ob comparator !-

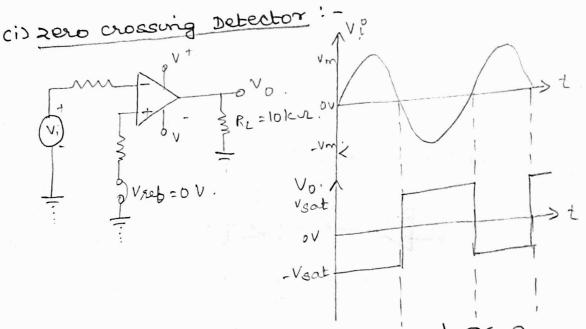

i) zero crossing Detector.

ii) window Detector.

iii) Time marker generator.

iv) phase meter.

The baric comporator can be ired as a zero crossing detector provided that vreb set to zero. The circuit is also called sine to saware vous generator.

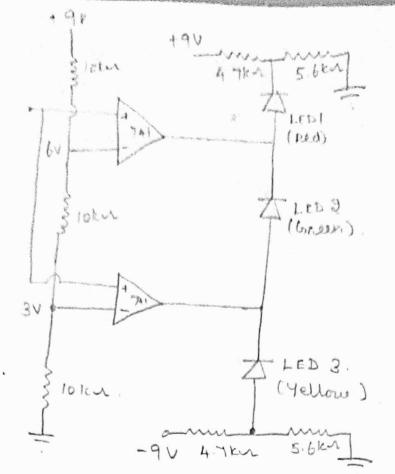

window Detector circuit is used to mork (ii) window Detector: the instant at which an unknown input is between two threshold levels. 3 indicators are

| ured.                                                            | Yellow LED 3     | GREEN LEDZ       | Red LED 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14 |

|------------------------------------------------------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Input(volts)  Less than 3 V  Between 3 V & 6 V  Greater than 6 V | OM<br>OFF<br>OFF | 066<br>0N<br>066 | obb on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                                                                  |                  |                  | The second secon |    |

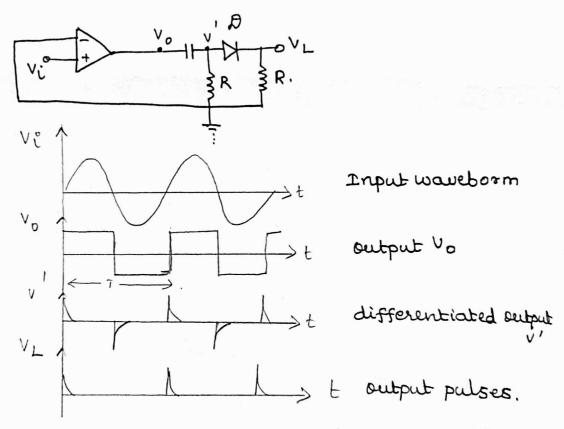

Time Marker Generator :-

=) The output of the Zew-crossing detector is differentiated by an RC Circuit (RC<CT)

=> The voltage v' is a series of the & -ve pulses

=) The negative portion is clipped abb abter paring

2

through the diode & and the waveborn VL. The Sinuroid has been converted into a train of the Pulses of spacing T and may be used for triggering the monoshots, SCR, sweep voltage of CRT etc.

#### Phase Detector:

phase angle between the voltages can also be measured using the previous circuit. Both voltages are converted into spikes and the time interval between the pulse spikes of one input and that of the other is measured, one can measure phase angles from 0° to 360° with such a voiscuit.

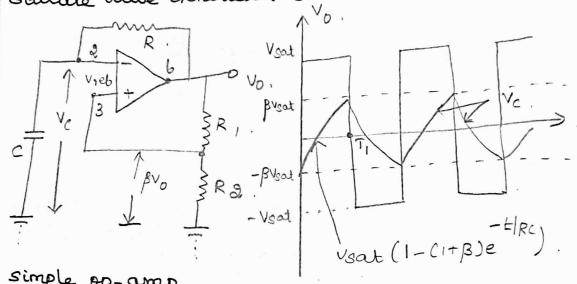

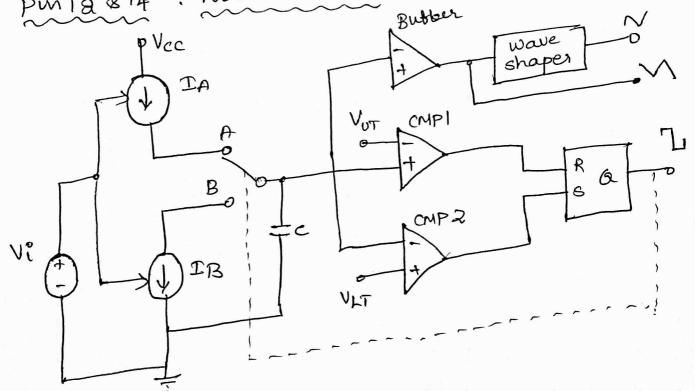

Sauare wave Generator (Astable Multivibrator)

simple op-amp Savare wave generator

waveforms.

=) It is also called free running oscillator. = Ra of the output is fed back

to the (+) input terminal.

- =) Reberence voitage Vreb is BVo. It takes + 13 Vsator

- -BVsat. =) The output is fed back to the (3 input terminal) abter integrating by means of low pars Rc combination

=) At instant of time, when the output is at + Vsal.

the capacitor starts charging towards + Vsal

through R.

=) The voltage at the (+) input terminal is held at +BVsat by R, & R& Combination. This state continues charges on c rises, until it has exceeded +BVsat, the reberence voltage.

=> voltage at the (-) input terminal becomes

greater than this reberence voltage, the output is

- veat. voltage on the capacitor is + B veat.

=> It begins to discharge through R, charges

toward - veat.

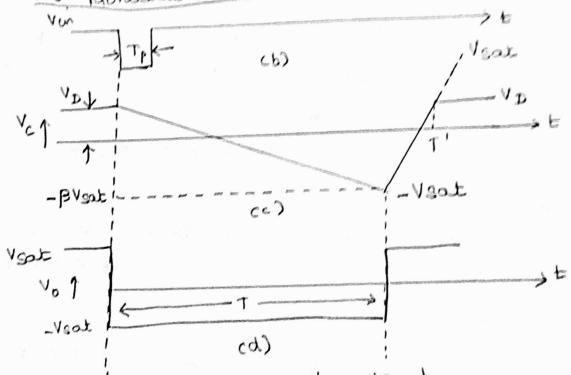

Voltage across the capacitor,  $V_c(t) = V_f + (V_i - V_f)e^{-t|Rc}$

Final value Vf = + Vsat.

Initial value Vi = -B Vsat.

-thro

V<sub>c</sub>(t) = Vsat + (-BVsat - Vsat)e V<sub>c</sub>(t) = Vsat - Vsat (1+B)e - HRC

At t=T1, voltage across the capacitor reaches

BVsat & Switching takes place. -T1/RC

Vc(T1) = 13 Veat = Vsat - Vsat (1+13)e.

$T_1 = Rc \ln \frac{1+\beta}{1-\beta}.$

Total time period  $T = RT_1 = RC \ln \frac{1+\beta}{1-\beta}$ . If  $R_1 = RR$ ,  $\beta = 0.5$ ,  $T = RC \ln 3$ .

R1 = 1.16 Rg. T = 2RC. The olp swings from +Vsat to -Vsat. Vo peak to peak = 2 Vsat.

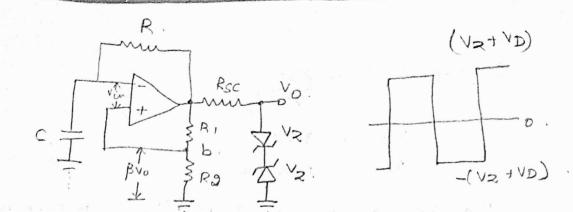

use of back to back zener diodes

Peak to peak output amplitude con be varied by varying the power supply voltage. A better technique is to use back to back zener diodes.

Vo (peak to peak) = 2 (U2+VD).

RSC -> limits the current drawn from the opening.

Problems: -

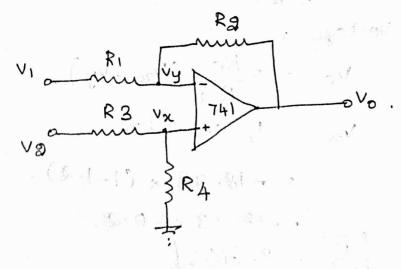

Find the Following for the given op-amp differential amplifui: i) The gain of the amplifies (ii) The input resistance iii) Destput voltage, when the inputs one Isin (2000+) V & I.2 sin (2000+) V and the R1 = R3 = 1.2km, Ra = R4 = 2akm.

The gain ob inverting amplifier is same as that ob differential amplifies.

(ii) Input resistance: with Vy = OV,

Inverting amplibier, input veristance is.

similarly Vn = OV,

Non inverting ampliture, input resistance is,

iii) output voltage =

$$V_0 = 3.666V$$

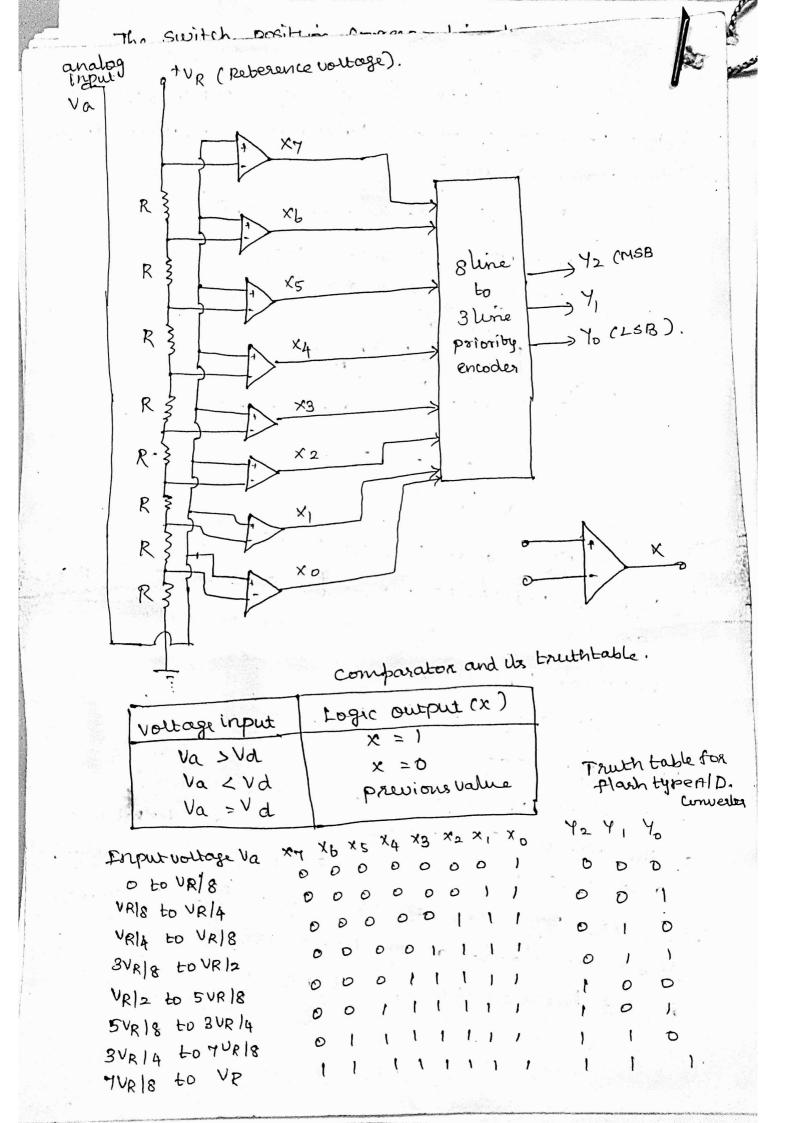

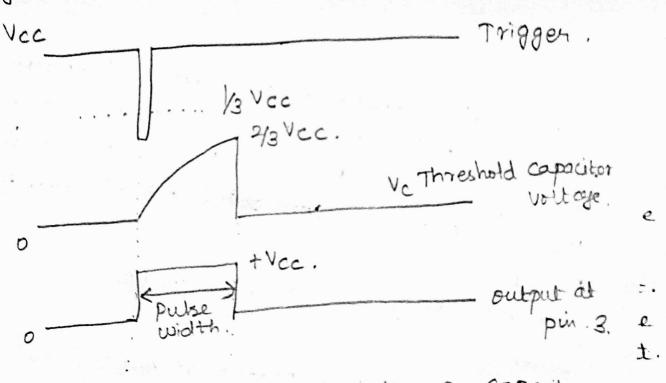

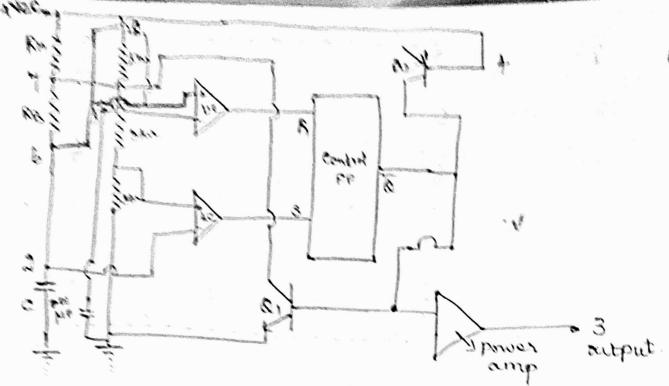

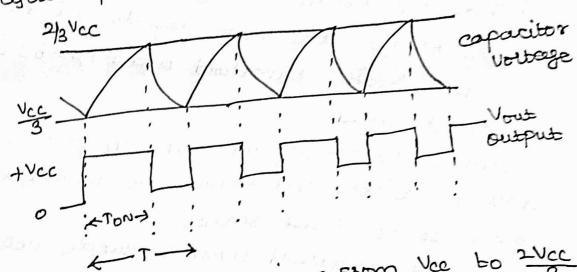

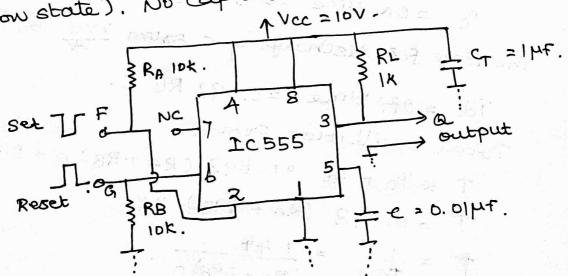

#### APPLICATION ICS: