#### **Department of Electronics and Communication Engineering**

**Regulation 2021**

III Year – V Semester

EC3552- VLSI and Chip Design

# UNIT-1

#### MOS TRANSISTOR PRINCIPLES

Introduction to Mos Transistor:

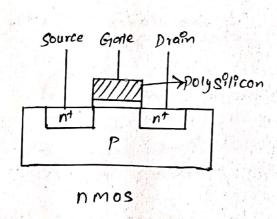

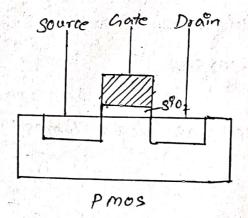

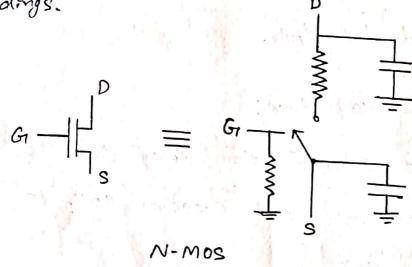

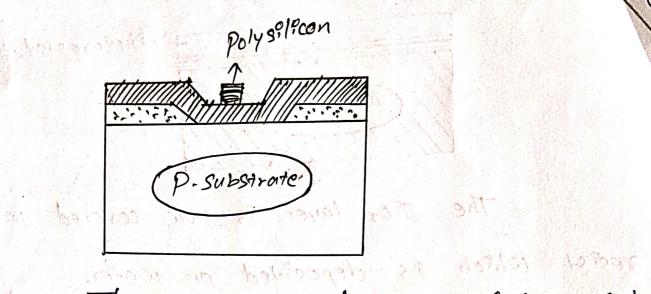

- A Metal-oxide - Semiconductor (MOS) transistor is formed by superimposing multiple layers of conducting and insulating materials like a sandwich-like structure.

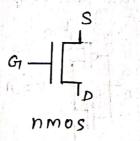

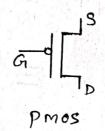

- The 2 types of transistors - nmos & Pmos.

- CMOS (complementary Mos) is a technology used in manufacturing of Ic and processors. CMOS combines both nMOS & Pmos on a single chip.

- The Mosfets are simply called as FETs.

- The nt and Pt regions indicate heavily doped nor P type silicon.

- Each transistor consists of a stack of conducting gote, insulating stor layer (glass), & substrate or body.

#### Mos as switch:

- The gate terminal acts as a control input as it can affect the electrical current between source and drain.

- So Mos transistors can be used as on/off Switches. When gate of nmos is ',' transistor ge on, & Vice-versa.

#### CMOS as Logic Gates:

By using the switching property of mosfer, basic logic gates function can be acheived using cmos.

NOT

$$\begin{array}{ccc}

A & & & & & & & & & & & \\

A & & & & & & & & & & \\

B & & & & & & & & & \\

\end{array}$$

AND

- Other than this, the cmos is also used to realize the complex logic gates and 3 input gates.

#### Ideal I-V characteristics:

- The Mos transistors are voltage controlled devices. i.e., A voltage on gate terminal induces a charge between source and drain.

- The charge is dependent on Vas. The current IDS is dependent on both Vas and Vos. Their relationship can be explained using the desiration

$$I_{DS} = \frac{Q_{c}}{Z} \longrightarrow 0$$

Ove - Charge Induced In channel

2 - electron transit tome

$$Z_{Sol} : \frac{L}{V} \longrightarrow \mathfrak{D}$$

1 - Length of channel

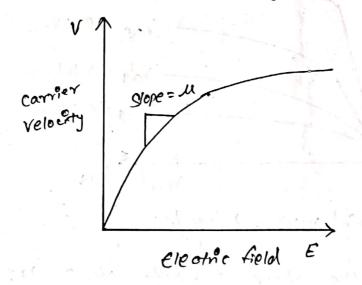

V- Velocity of holes / electrong

U - electron/hole mobility

Eds - Electric Apold between source-Drain.

$$Eds = \frac{V_{DS}}{2} \longrightarrow \triangle$$

$$V = \mathcal{U} \cdot \frac{V_{DS}}{L} \longrightarrow \mathbb{S}$$

- The mobility of electrons & holes at room temperature is

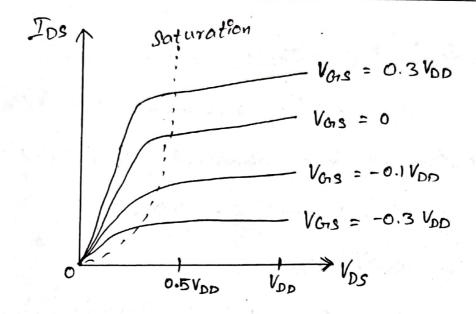

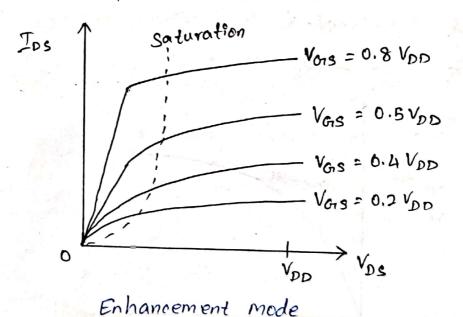

Depletion mode

Ideally, the above characteristics are to be obtained. But it is impossible to realise these using the practical enhancement and depletion mosfets.

Non-Ideal I.V effects:

The various non-ideal I-v effects that can influence the electrical characteristics are:

- 1. Channel length Modulation

- 2. Body effect

- 3. Drain- Induced barrier lowering

- A. Subthreshold conduction

- 5. Gate oxide tune! Ing

Channel Length Modulation:

As the voltage across Mosfet Increases, the channel length can effectively Shorten due to electric field at drain and of channel.

This effect leads to an increase in drain current.

#### Body Effect:

The body effect, also known as back-gate effect arises from Influence of Voltage applied to Mosfer's Substrate or body terminal. This effect can lead to threshold Variations.

Change to Laborate

## Drain Enduced Barrier lowering:

It is a phenomenon that occurs in mosfer as the thought of transistor decreases. It refers to the reduction of effective energy barrier at Source-Drain region under influence of drain voltage.

#### Sub-Threshold Conduction:

When the voltage applied to gate is below threshold voltage, the channel 9s not fully formed & only small leakage current called Sub threshold leakage current flows between source-Drain terminals.

Grate oxide tuneling:

It is a process where elections/holes tunnel through the oxide layer, allowing the charge carriers to flow between the gate and channel. The two mechanisms of tuneling are:

- Direct functing

- Fowler Nordheim tunoling.

# Drain Punch - through:

When a high voltage is applied to drain, the depletion region around drain may extend to source, causing the current to flow irrespective of gate voltage is called as drain puch - through.

THE STATE OF THE S

to all the course was a set of the second

It occurs due to.

- 1. Higher voltage to gate

- 2. Arcing across the thin oxide.

Mosfet Characteristics under Stathe & Dynamic Conditions:

The vortous static and dynamic Characteristics

of Mosfet are lested below:

#### State characteristics:

- 1. Threshold voltage (Vin)

- 2. Drain source on resistance (Ros)

- 3. Drain Current (20)

- 4. Output characteristics (ID 18 VDS)

- 5. Transfer characteristics (ID VS Vas)

#### 1. Threshold voitage:

The minimum gate to Source voltage required to establish a conducting channel between the source and drain terminals. It determines the onloss state of Mosfer.

#### 2. Drain Source on resistance:

The resistance between the drain and source terminals when the Mosfet is in on-state. It

affects the power dissipation and efficiency of the device.

#### 3. Drain Current:

The current flowing from the drain to the Source terminal under a given gate to source Voltage (Vas) and drain to source voltage (Vps).

It depends on the applied voltages and the characteristics of MosfeT.

#### 4. Output characteristics:

The plot of ID vs VDs at a constant Vas is called as output characteristics. It shows the region of operation, such as the saturation region and triode region.

# 5. Transfer characteristics:

The plot of drain current versus gate to source voltage at a constant Vas is called as transfor characteristics. It indicates the threshold

voitage, Mosfei's behaviour on on/off states and the device's transconductance.

Dynamic characteristics:

The dynamic characteristics of a MOSFET are:

- 1. Gate Capacitance

- 2. Switching time

- 3. Output capacitance.

- 4. Miller effect

## 1. Gate Capacitance:

The Capacitances between gate-source and gate-drain is called as Gate capacitance (Cas & Cap)

They play a crucial role in charging &

discharging of the gate voltage, & Speed of Mosfer.

#### 2. Switching time:

It refers to the time required for the Mosfer to transition between the ON & Off States. It depends on gate capacitance, gate resistance & lead.

# 3. Output Capacitance:

The Capacitance between the drain and the Source terminals when the Mosfet 9s 9n Off State 9s called output Capacitance.

It affects the transient response and energy losses during switching.

#### 4. Miller Effect:

It refers to the increase in effective gate Capacitance due to the voltage amplification between the input and output terminals of Mosfer.

It affects the switching speed & can lead to oscillations.

#### Norse Margin:

Noise margin is the allowable input gate voltage so that the output will not be corrupted.

Age to the the thirty of

# Technology Scaling:

It refers to the process of reducing the size of electronic devices and components, such as transistors, Ic and other semiconductor devices.

Technology Scaling is often assocrated with Moore's law, which states that the number of transisters on a chip doubles approximately every two years.

Scaling down the size of transpistors & other components leads to improved device performance. Smaller transpistors can switch faster, resulting in higher operating frequencies.

As the Size of transistor shrinks, it requires lesser power to switch between on lote states.

The VISI Technology scaling is aimed at acherving the smaller line widths and size for higher packing density.

# Merits or scaling:

- 1. Scaling allows integration of more components on the same chip area.

- 2. Improved switching performance

- 3. Shorter signal propagation delays.

- 4. Ethanced corcust performance

- 5. Reduced power consumption

- 6. Cost reduction in manufacturing of the somiconductor devices.

- 7. Ability to integrate more functionality on a single chip.

- 8. Leads to new device architectures, novel materials and advanced monufacturing techniques.

- 9. Lesser learage currents and lesser manufacturing complexities.

#### Demerits:

1. Even though overall power consumption reduces power consumption per unit area increases.

Mirror with a training to the state of the

- 2. Derice gets heated up during operation.

- 3. Carrier mobility reduces which inturn reduces gain of the device.

- 4. Reduced Conductor Size decreases the current carrying capacity.

- 5. To reduce heat generated, forced cooling is

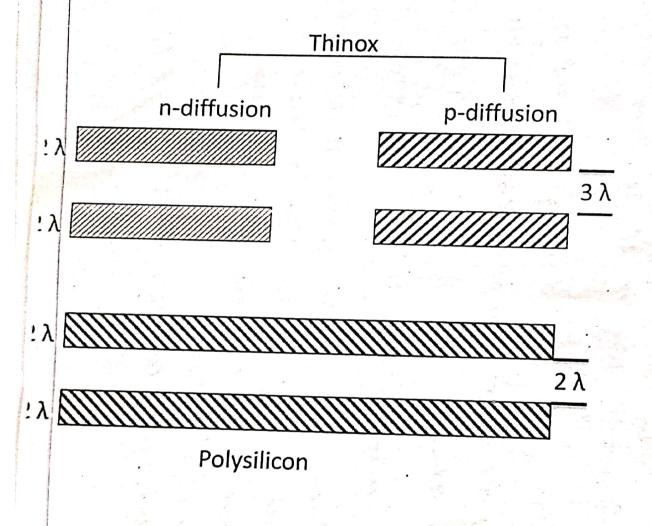

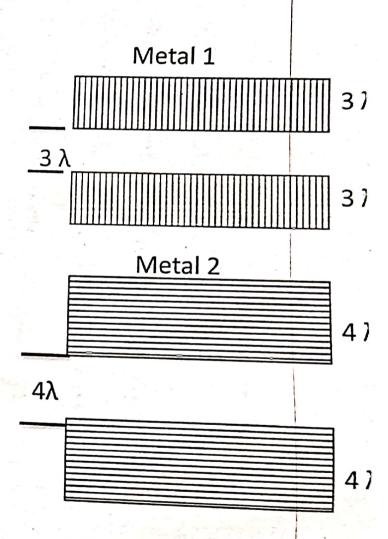

Lambda based Design Rule:

It is a methodology used in semiconductor manufacturing to establish a scalable measurement unit and spacing requirements.

The Lambda (1) represents a reference length or pitch, which is typically chosen based on the process technology node or the minimum feature size of the Semiconductor process.

This method simplifies the design process by expressing dimensions, spacing and other dayout in terms of A.

The few aspects of Lambola based design

#### Lambda Definition:

Lambda represents a fixed reference length or pitch. It is derived based on the process technology node or minimum feature size.

one lambda might be defined as sonm.

# Dimensions and Spacing:

Instead of specifying a metal wire width as 0.25 Lm, it is expressed as 5% (assuming 1% = 50 nm).

Similarly, Spacing between two adjacent features might be defined as 3%.

In General, it is to be noted that the value of a varges for each device and designers can fix the value to their convenience.

# Modes of scaling:

- 1. Lithography Scaling

- 2. Transpstor Scaling

- 3. Interconnect scaling

- 4. Material Prinovations

- 5. 3D Integration

# Scaling factors for device parameters:

- 1. Length & width scaling factor.

- 2. Voitage scaling factor

- 2. Current scaling factor

- 4. Performance Scaleng factor.

# Grate Capacitance:

The gate capacitance refers to the capacitance associated with the gate terminal of MOSFET. It consists of a components - Cas & Cap.

Parasitic Capacidance:

The paragitic capacitance of Mosfet refers

to the capacitance that exist between various

terminals and regions of the device.

These parasitic capacitances have an impact on the device's performance and can affect its high frequency behaviour.

The components of gate capacitance are  $C_{GS}$ ,  $C_{GD}$ ,  $C_{GB}$  and  $C_{DS}$ .

Power Consumption:

The Storlic CMUS gates are very power efficient. They dissipate nearly zero power while idle.

The power dissipation in a cmos is

P = VDD. IDe

where,

VDD - Power Supply voltage

Ire - Current drawn from power Supply.

The CMOS power dissipation is categorized into

- Static power dessipation

- Dynamic power dissipation.

Static power Dissipation:

It refers to the power consumed by a device when it is in a Static or idle state, regardless of any active signals being processed.

It arises from the leakage currents that flow through transistors and other components.

The major causes of static power dissipation

- 1. Subthreshold Conduction through Off transistors

- 2. Tunneling current through gate oxide

- 3. Leakage current through reverse biased diodes

The Static power dissipation is given as:

Pstatic = Istatic VDP.

timo and

The static power dissipation is due to leakage current flowing through the reverse brased functions of transfistors.

The leakage current per unit drain area ranges between 10 to 100 pa/um? The total static power dissipation is given as:

Protal State = = I I State . VDD

Dynomic Power Dissipation:

The dynamic power dissipation refers to the power consumed by a device during its active operation, Specifically during the switching of signals and the charging and discharging of internal capacitances.

It is given by the equation,  $P_{dynamic} = 0.5 \times C_L \times V^2 \times f$

Where,

Paynamic - Dynamic power dissipation

CL - Load Capacitance

V - Supply voitage

f - frequency of signal transitions.

The various factors that contribute to the dynamic power dissipation are:

1. Capacitive charging / discharging

2. Clock power

3. Short- Circuit power

4. Activity factor

Reducing the dynamic power dissipation is Crucial for improving the energy efficiency. The Various techniques employed to minimize dynamic power are:

- 1. Clock gating

- 2. Voltage Scaling

- 3. Low power Circuit design.

Short Circuit power Dissipation:

It Prolicates the power dissipation due to Short Circuited current in an unloaded inverter. The S.c power dissipation is given as

$$P_{SC} = \frac{k}{12} \left( V_{DD} - V_{t} \right) \frac{3 \ell_{rf}}{\ell_{p}}$$

Where,

tp - period of 9/p waveform

trf - Rise time of 9/p waveform

K - Constant.

Need to estimate power dissipation:

The power dissipation affects

- 1. Performance

- 2. Reliability

- 3. Packaging

- 4- Cost

- 5. Portability.

factors influencing cmos power Consumption

There are 3 major sources of power

dissipation,

Parg = Pswitching + Ps.c + Pleahage

Techniques to reduce power consumption:

The following techniques can be used to

roduce the power consumption,

- 1. Reduce voltage

- 2. Reduce switching actority

- 3. Reduce Physical Capacitance

- 4. Ordering of Input Signals

- 5. Mananizing glitching activity

- 6. Manimizing number of operations.

# Low Power optimization:

The low power optimization technique of MOSFET Ps aimed at reducing the power Consumption

Some of the commonly used techniques for low power optimazation are:

1. Threshold voltage Adjustment:

By adjusting the threshold voltage of Mosfer, the power consumption can be lowered. Lowering the threshold voltage reduces the leakage Currents and Static power dissipation.

2. Scaling down Supply Voltage:

Reducing the supply voltage of mosfer lowers the power consumption.

3. Subthreshold operation:

Operating the moster like vas below the threshold voltage can reduce the power consumption significantly.

4. Multi- Vt Techniques:

Using multiple throshold voltage transistors

9n a single corcuit allows better power optimil--zation.

# 5. Power Gating:

Power gating Puvolves selectively turning of the power supply to specific blocks or components of the corcuel when they are not in use.

# 6. Clock gating:

The clock signals are sclentively enabled or disable based on the activity of circuit blocks.

All the above mentioned techniques can be applied individually or in combination depending on the specific requirements of the application.

#### UNIT-2

#### COMBINATIONAL LOGIC CIRCUITS

#### Introduction:

The combinational logic circuits are the digital circuits that perform a specific logic operation based on the current input Values.

The output of a combinational logic circuit depends only on the present input Values and not on any previous inputs.

# Propagation Delay:

Propagation delay refers to the time it takes for a signal to travel through a circuit or a component from its input to its output.

It is a measure of the time delay experienced by a signal as it propagates through the circuity.

In cmos logic circuits, the propagation delay is mainly due to critical paths. It is nothing but the logic paths through the cmos circuit.

The delay estimation can be done through:

1. Rise time:

The time required for a waveform to rise from 20% to 80% of its steady state value. It is denoted as 'ti.'

#### 2. fall time:

It is the time required for a waveform to fall from 80% to 20% of its Steady State value. It is denoted as to.

#### 3. Edge Rate:

Edge rate is the average of rise time and fall time. It is denoted as trp.

$$t_{rf} = \frac{t_{r} + t_{f}}{2}$$

Propagation Delay time:

It is the maximum time from the input crossing 50%.

It is denoted by tpd.

Contamination Delay time:

The contamination delay time is the minimum time from input crossing 50%. to the output crossing 50%.

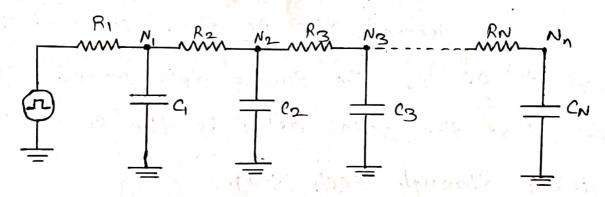

Rc Delay Model:

The RC delay model is a method used to estimate the propagation delay of signals through interconnects (wires) in a circuit.

The Rc delay model assumes that the Interconnect can be represented as a Rc network, where the resistance of

the wire and the capacitance represents the inherent capacitance between the wires and its Surroundings.

$$G_1 - d = G_1$$

$G_2 - G_3$

$G_4 - G_4$

$G_5 - G_6$

$G_7 - G_8$

$G_7 - G_8$

$G_8 - G_8$

P-mos

When multiple transistors are in series, the equivalent resistance is the sum of each

and individual resistance. When multiple transistors are in parallel, the equivalent resistance is clower.

The RC delay model 9s often used 9n conjunction with other models, such as Elmore delay model to estimate the overall delay of the signal path 9n a corcuit.

#### Elmore Delay Model:

The Elmore delay model is a widely used method for estimating the signal propagation delay in electronic cricuits, particularly Rc networks.

It provides a simple and efficient way to estimate the delay based on the Rc time Constant.

In the Elmore delay model, the delay is calculated as the sum of the products of resistance values and capacitance values along the signal path.

The model assumes that the signal propagates as a series of charging and discharging RC Stages.

In general, the Rc 49me constant is referred to as 7. The Elmore delay modes considers that the total delay is the sum of the delays through each stage.

The disadvantage of Elmore delay modes? is that, it assumes all the capacitances are charged and discharged simultaneously.

are purely resistive, disregarding inductance effect.

# Parositic Delay:

The parasitic delay refers to the additional delay introduced in an electronic circuits due to parasitic elements present in the circuit.

The parasitic elements includes parasitic capacitance, parasitic capacitance, parasitic resistance & moluctance. The delay of gate when it drives zero load is parasitic delay. Logical Effort Model & Effort Delay:

The logical effort model is a design methodology used to optimize the performance of digital circuits.

The effort delay refers to the delay associated with driving a lood in digital circuits.

The Jog?cal effort is a measure of the relative sizing of the gate compared to a reference gate.

The Logical effort is also defined as the ratio of input capacitance of the gale to the input capacitance of an inverter which delivers the same output current.

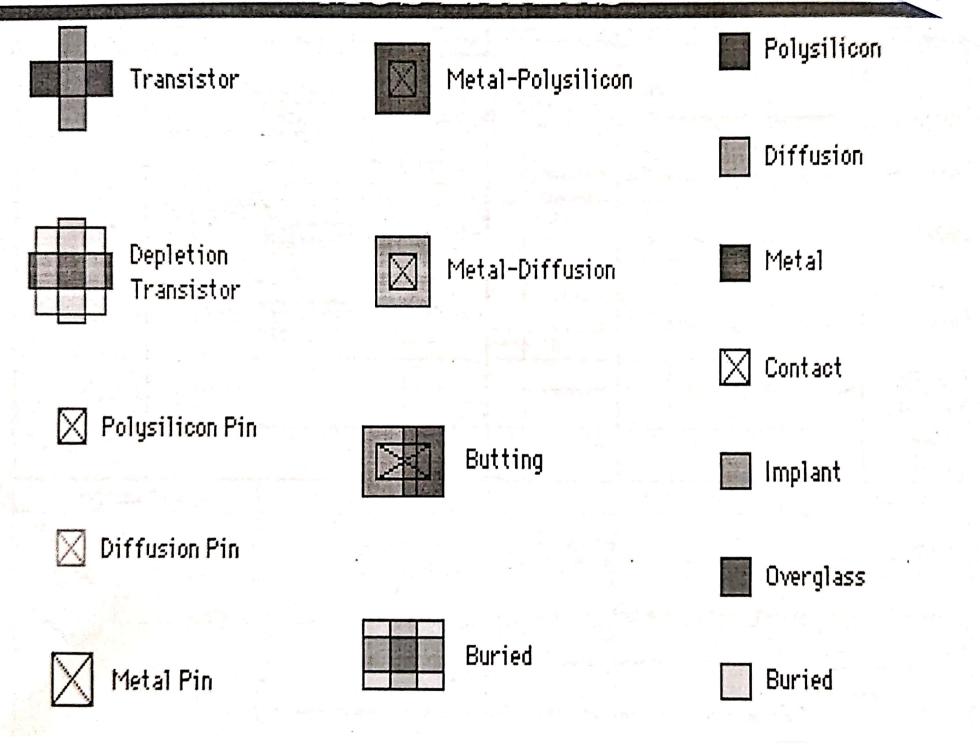

## Stick Diagram:

A stick diagram is a graphical representation used in Ic design to illustrate the Jayout of a circuit using simple shapes and lines.

The main purpose of the stack diagram is to provide a visual representation of the circuit layout that can be used to analyse and optimize the circuit for performance, area and other design considerations.

The strck diagrams are useful in corry understanding of circuit design rather than doing detailed. Layout implementation.

In recent days, the stick diagrams have became less prevalent as moder Ic design proctices such as advanced cap tools are used for more accurate and detailed representations.

However, the Stick diagrams Itill serves as a valuable tool and and an understanding the fundamental principles of Ic layout design.

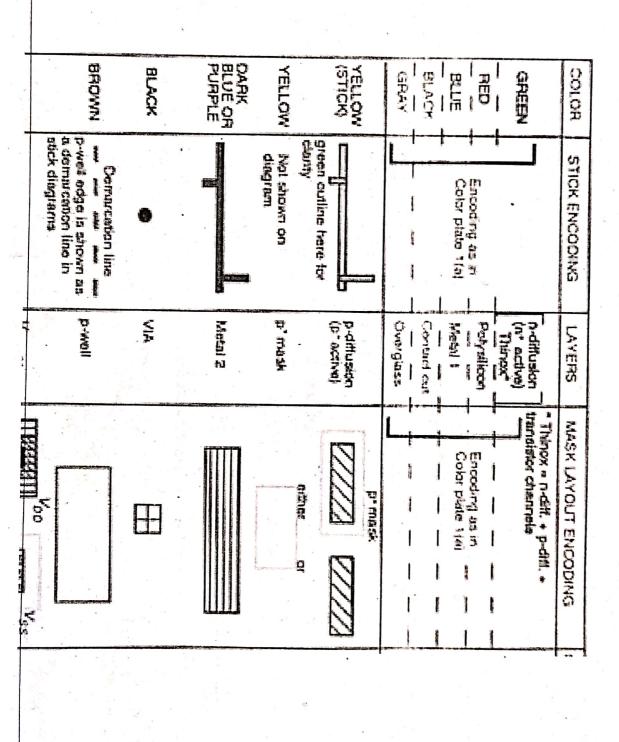

The Strck dragrams are used to convey the layer information through the use of colour code.

# Colour codes:

Green - for n diffusion & other thin oxide regions. Only i paysilicon layer is involved. Blue - only one metal layer is involved.

Yellow - Implant

Black, Brown - Contacts.

# DESIGN RULES

| n-type depletion<br>mode translator<br>nMOS only | n-type<br>granacement<br>mode transistor<br>Transistor length | FEATURE          | SHOWN  | AETTOM. | GRAY           | BUACK       | 860                       | GREEN               | COLOR          |

|--------------------------------------------------|---------------------------------------------------------------|------------------|--------|---------|----------------|-------------|---------------------------|---------------------|----------------|

|                                                  | S C                                                           | FEATURE          | 0      |         | NOT APPLICABLE | 0           |                           |                     | STICK ENCODING |

| Source, drain and gate labelling will not not    | G S G D                                                       | RE (STICK)       | Buried | implant |                | Contact cut | Polysiticon               | in: active) Thinage | AG LAYERS      |

| in not normally be shown                         | S G C                                                         | FEATURE (SYMBOL) | X      |         |                |             | n word - n-diff - transis |                     | MASKIAWA       |

|                                                  | 10 No.                                                        | FEATURE (MASK)   |        |         |                |             | do Charnots               | ,                   |                |

| in we have                                       | o o                                                           | (MASK)           | 200    | Z       | Z<br>G         | 2           | ₹ .                       | OF LAYER            |                |

# **Encodings for CMOS process**

#### < 2\lambda from polysillcon 2% minimum decrease in width Diffusion is not to Thinox mask = union of n-diffusion, P-diffusion, and channel regions Design rules for transistors 67 X 67 implant a minimum of 21 beyond Transistor channel Polysilicon to extend\_ diffusion boundaries (depletion) (width obrastant) nMOS depletion mode transistor Minimum size transistors to extend 21, minimum beyond Extensions and separations another transistor channel" in all directions (and beyond polysilicon Separation from with buried contact) implant to 2 (enhancement) Implant for an PMOS I 21 x 21 2\lambda minimum M Separation from contact cut (enhancement) 27.x 27. NAOS 2 minimum to transistor

# Layout Diagrams:

The Layout olfagrams are used in Ic design to illustrate the detailed arrangement and placement of circuit components on a chip.

These diagrams provide a visual representation of the physical layout of the circuit components on a chip.

Layout disagrams are created using the specialized computer-aided design (CAD) tools that supports the layout design process.

The Interconnections between the components such as metal traces and contacts are also Included in the layout diagram.

They help in identifying the potential design issues such as overlapping, spacing violations etc., It also ensures power, performance & area requirements.

There are number of approaches to describe the design rules. They are:

- 1. Micron design rule

- 2. Lambda design rule

#### Micron Design rule:

The micron design rules are given as a light of minimum feature sizes and spacings for all the marks required in the given process.

# Lambda Based Design Rule:

The A refers to a und of longth that is equal to the minimum feature size of the Process technology being used.

This method simplifies the specification of design miles by expressing them in terms of lambala rather than using absolute values.

#### Contact cuts:

The contact cuts provide the electrical connections between different layers of Ic, and allows the signals to pass vertically from one layer to another.

The 3 possible approaches for establishing contacts between polysilicon and diffusion in NMOS circuits are:

- 1. Poly to metal & metal to diffusion

- 2. A bunged contact poly to diffusion

- 3. A butting contact poly to diffusion using metal.

Static Logic Gates:

The state logger gates uses only state comos technology. It is widely used in modern Ie dechnology because of their low power consumption.

The 2 most commonly used types of Static legic gates are:

1. SHORE CMOS NAND gate

2. Static CMOS NOR gate

Bubble Pushing:

Bubble pushing is a technique used in digital circuit to optimize gates and to reduce the propagation delay. 1 Land a transform

The term bubble refers to the logical inversion of a signal represented by NOT gate.

De-Morgan's Law

The main goal of bubble pushing is to reduce the complexity of circuit by introducing additional bubbles in the path & reducing the number of logic levels or stages that the signal needs to pass through which ultimately reduces the delay.

Agn. I was the good

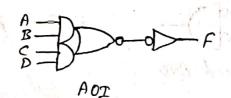

# Compound Gates!

The compound gates are the logic gates that can perform more than a single basic logic operation. They are constructed by combining multiple basic logic gates in a specific configuration to implement a more complex logic function.

Dynamic Logic Gates: Vs Static Logic Gates:

| 9.20 | Aspect               | Static                                                              | Dynamic                   |

|------|----------------------|---------------------------------------------------------------------|---------------------------|

| 1.   | Operation            | output is directly connected to input without any storage elements. | temporanty (part          |

| 2.   | Power<br>Consumption | Power efficiens                                                     | Requires more power.      |

| 3.   | Speed.               | Lower propagation delay.                                            | Hegher propagation delay. |

|      | Area                 | lequires more splicon area.                                         | Comparatively less.       |

| 5    | . Complexity         | Easy to design                                                      | Complexi                  |

Radroed Carcuit:

The ratioed Arcuit uses a combination of parallel transistors. to emplement the basic logic gates.

The key feature of rational circuits is that it reduces the number of transistors required to implement a given logic function.

It also has a disadvantage of reduced robustness and increased power dissipation.

It is used in current mirrors, differential amplifiers, ADC and DAC circuits.

## Pass Transistor Logic:

The pass transistor Logic (PTL) is a type of Digital logic design used in Ic for implementing the logic functions, which comes as an alternative for traditional Static cmos.

In PTL, transistors are used as switches to allow or block the flow of signals which results in realization of different logic gates and circuits.

The basic building block of PTL is a pass transistor which is a type of Mosfet. The FET acts as a switch and allows the passage of input signal when it is activated. They don't need any intermediate gates like NAND or NOR.

There are 2 types of pass transistor

Lawrence 💖 extension

# configurations:

- 1. Transmission Gate (TG)

- 2. Pass Gate Logic (PGZ)

# Tronsmission Gate:

The transmission gate consists of a pmos and an Nmos connected in parallel. The gates are controlled by complementary control signals. When control signals are active, the pass transfistor behaves as a closed switch & vice versa.

Pass Gate Logic:

It is uses a single Mosfet as a pass transfistor, & Controlled by a single control signal. When control signal is high, pass transfistor is on a vice versa.

The following are the advantages of PTL:

- 1. Reduced transfistor count

- 2. Lower power consumption

- 3. Higher speed

# Dower Dossipation:

The power dissipation is the amount of energy consumed or Jost by the circuit over a certain period of time.

Low power Design Principles:

It is a set of guidelines and techniques used by It designers to minimize the power

Consumption in Ic and electronic systems. Some of the key low power design principles are:

- 1. Clock gating

- 2. Power gating

- 3. VoHage gating

- 4. Sub-Threshold operation

- 5. Adaptive voltage scaling.

- 6. Sleep mode and power modes

- 7. Efficient memory design

- 8. Optimal transistor sizing

Taking core of the above mentioned principles will dractically reduce the power consumption of the ge circuits.

## UNIT-3

# SEQUENTIAL LOGIC CIRCUITS &

#### CLOCKING STRATEGIES

#### Introduction:

The sequential logic carcuits are a type of digital logic carcuits in which the output not only depends on the current input but also on the previous stages of the carcuit.

I love got int

Hence, the sequentfal logic circulats needs

the memory elements to store information and to

use in future.

The fundamental building block of a sequential logic circuit is flip-flop, which is a bistable multivibrator capable of holding one of two stable states: o or 1. The commonly used flip-flops are SR ff, D ff, Jk ff.

By combining the Air flops and logic gates (AND. OR, NOT, etc)., more complex sequential logic circuits such as counters, registers, are formed.

State Latches and Registers:

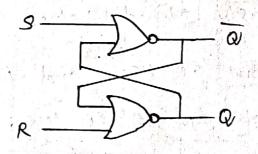

The State latch is a simple storage clement that can store one bit of data and retain it as long as power is supplied. It is composed of cross coupled NOR or NAND gates.

The two most common types of Static latches are

1. SR latch

2. D Latch.

A static Register is a collection of flip flops connected togother to store multiple bits of dada simultaneously. The number of fift-flops determines its capacity.

SR FIPP Flops:

The SR fisp-flops also known as

SEH-Roset fisp-flop. Is a basse type of

Sequential logic circuit. It is a bistable multivebrator, meaning it has two stable states, &

It can stay in one of these states until a

Control signal changes is state. The flip-flop has

2 inputs (S&R) and 2 output (a& & G')

| 9 | R   | Ø/  | ai      |

|---|-----|-----|---------|

| 0 | 7,0 | . 0 | Q'      |

| 0 |     | 0   | $J_{i}$ |

| 1 | 0   | Ţ   | O       |

| 1 | 72  | ×   | ×       |

Truth table

The x' in the last row indicates & undefined state, which should be avoided in practical implementations, because it leads to unpredictable behaviour.

#### Working:

1. When both inputs are low, the flip flop remains in its current state and there is no change in the output. This is hold state and it maintains the proviously stored value.

2. When S input is High and R is low, the output a school of is 1010. This is set state, where the output is forced to 1.

3. When Sis low and R is high, the cutputs of is low and O' is High, This is reset state, where the output is forced to O.

4. When both superis are high, output is undefined state.

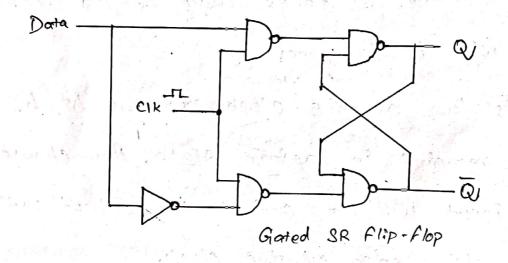

D FIRP - Flop:

The D flip flop, also known as the clara or Delay flip-flop 9s a type of sequential logic carcuit. It is a clocked storage element that stores one bit of data.

| Clk | D | Q | .Q/            |  |  |

|-----|---|---|----------------|--|--|

| 0   | X | 0 | <b>&amp;</b> ′ |  |  |

|     | 0 | 0 | 1              |  |  |

| 1   | 1 |   | 0              |  |  |

Truth table

## Working:

1. When the clock Input 95 low, the Mg. flop 9s 9n a hold state. The output retains 94s current state, regardless of data input. Q' also held in Hs previous State.

2. When clock 9s 1, 9t enters capture state. At this moment, a takes value of data suput and O' will be its reverse,

3. As long as the clock remains high flip flop remains in capture state. Any change In data input will not affect the output until the next vising edge of the clock.

A. When clock goes low, the flip-flop goes to hold storae, retaining the , a and a' at the last captured values

# Dynamic Latches and Registers:

A dynamic latch, also known as a clocked latch uses the concept of capacitor charging and discharging to stone the data. It requires an exceptual clock signal to contral its operation.

The most common type of dynamic latch is the Moster-slave latch, which consists of 2 cascaded stages, master and slave.

The Master Stage Consists of a transmission gate that connects the data input to internal node. The slave stage consists of an inverter that amplifies the signal storad in internal node.

A dynamic register is used to Store multiple bits of data using a Common Clock signal. But they consume more power compared to starfic registers.

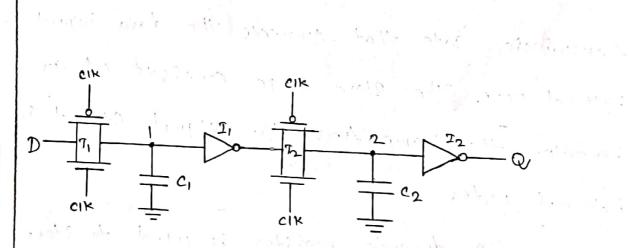

Dynamic Transmission- have tolge Triggered Registe

A transmission gate is a type of switch implemented using cmos. It acts as a pass gate, allowing signals to pass through when the gate is active and blocking them when it is inactive.

The primary advantage of dynamic transmission gate registers over static registers is that they require fewer transmistors, which leads to reduced area and power consumption.

When the imput is clock is zero, the input data is sampled on storage node 1, which has an equivalent capacitance of c, consisting

9

oster

of gate capacitance of I, the junction capacitance of T, and the overlap gate capacitance of T,

During this period, the slave stage 95 9n hold mode. On the rising edge of clock, 72 turns on and the value sampled on node I propagates to output Q, and node 2 stores the inverted version of node 1.

The set up time of this carcuit as

simply the delay of TG, and corresponds to the

time it takes node I to sample D input.

The hold time is approximately zero. The propagation delay is equal to 2 inverter delay plus delay of 12.

The disadvantage of dynamic transmission gate edge triggened registers is that the storage nedes has to be retrished at periodic intervals to prevent less due to charge leakage.

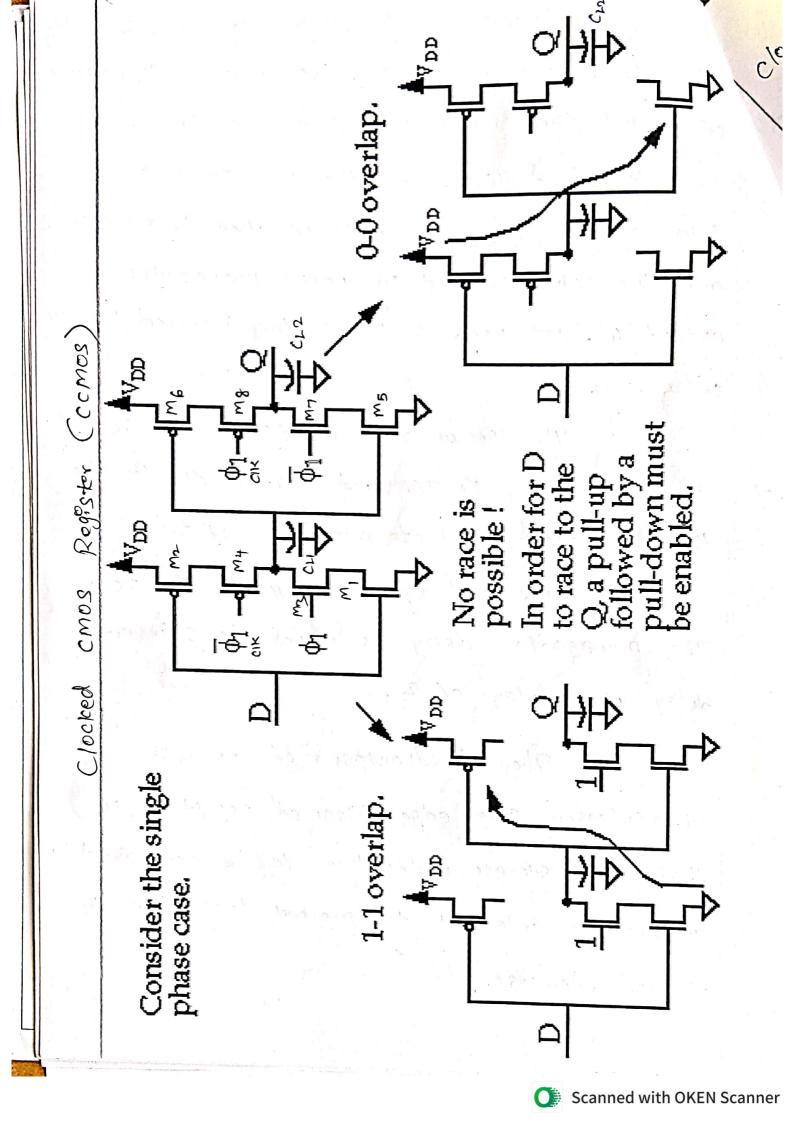

Clocked C-Mos Register:

When the CIX = 0, the master Stage

acts as an inverter sampling the invented

Version of D on the internal node X. The

Master stage is in the evaluation mode,

meanwhile, the slave section is in a hold mode

Both my and Mg are off, hence decoupling the

output from input. The output a retains its

previous value stored in C12.

The roles are reversed when Clic = 1.

The master section 9s in hold mode (Mz-Mz-Off)

and the (M-Mz is ON). The value stored on

CLI propagates to the output through the slave

Stage which acts as an inventor.

The main idea of pulse register 1s to construct a short pulse around the rising or falling edge of the clock. This pulse acts as a clock input to a latch.

## Popelining:

Pipe lining is a technique of diving the execution of complex digital circuits into smaller sequential stages.

Here, a complex digital corcuit 9s divided into multiple sequential stages and each stage performs a specific operation and passes it to the next stage. The output of one stage becomes the imput of the next stage and each stage operates on a different subscit of the data.

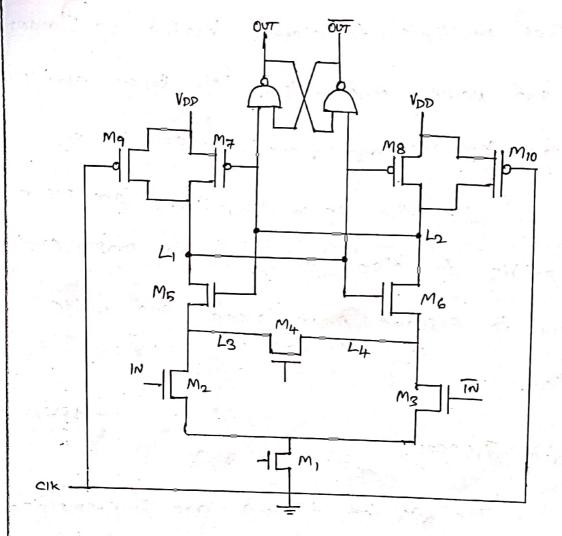

Sense Amplifier Based Register:

The sense amplifier based register is

Commonly employed in memory cells, register files and

other storage elements in VLSI. The primary purpose

of sense amplifier based register is to improve

the read and write performance of the memory

cell.

The conventenal flip-flops or latches

requires multiple transistors leading to larger area and power consumption. The sense amplifier is more compact and needs lesser power.

But the sense amplifiers are more susceptible to noise and requires proper control circuitiy to ensured proper read and write operations.

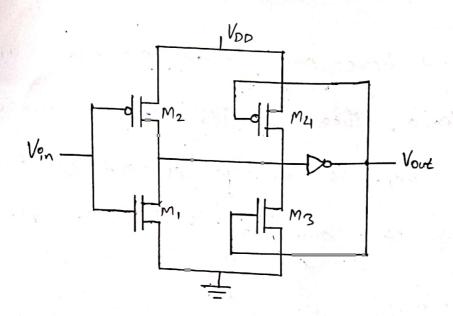

Schmidt Tragger:

The Schmitt triggers are implemented using transistors and other semiconductor devices. The 2 important properties of a schmitt

1. It responds slowly to a changing input waveform with a fast transition time at the output.

2. The voitage transfer characteristics of the device displays different switching throsholds for the and the input signals.

#### Working:

To turn and cmos soverter so to a schmitted trigger, hysteresis is introduced by adding possitive feedback. The possitive feedback provided by the additional pmos and Nmos creates two threshold levels.

Non- bestable Sequenteal Circuits:

The non-bisdable sequential circuits also known as combinational circuits are digital circuits.

that do not have any memory elements or feedback leops. These Circuits produce an curput that solely depends on the current Input Values and do not store any past Information about the supputs.

Monostable sequential Circuit:

The monostable sequential cocust is also called as one shot or pulse generator is a type of sequential cocust that has a single stable state and one unstable state.

The monosdable circuits remain in their stable state undil traggered by an external input Astable sequential circuits:

The astable sequential circuits

Continuosly switches between two unstable states

without any external control. Hence st generates

Continuous square ware or pulse toain.

when power is applied, it starts to oscillate between its two unstable states, creating a periodic output wareform.

Timing classification of Digital Systems:

In general, the digital systems can be classified based on their timing behaviour,

9nto 3 main categories as!

- 1. Synchronous

- 2. Asynchronous

- 3. Mezed teming systems.

#### Clock Stew:

The clock stew refers to the difference in amiral time of a clock signal at various elements within a digital system.

In a synchronous degetal system, all the components are differ by a common clock signal.

But due to routing lengths, & temperature variations,

the clock signal may not arrive simultaneously sort at all parts of the circuit.

Sources of Clock Skew!

The clock stew sources can be classified as:

- 1. Systematic

- 2. Random

- 3. Diff

- 4. Titter.

#### Systematic'

Systematic Clock skew is that portion which exists even under nominal conditions.

#### Random:

Random Stew is caused by manufacturing variation which affects wire width, therness and Spacing.

#### Dinft:

Diff show is caused by environmental

variations which occurs very slowly.

#### Titter:

Titter show is coused by high frequency environmental variations, particularly power supply noise.

# Logical clocking handbille has inside

A logical clock Ps a gignal with no clock show. It produces ideal signals with no show used by logic closigner when describing a HDZ.

# Single Phase Clock:

The single phase clock or traditional clock of a single edge clock that alternates between two states in a regular pattern.

The clock frequency 9s determined by

the time person between rising or falling edges

of consecutore signals.

Two-phase Clock:

The two phase clock has 2 seperate non-overlapping clock signals. During 137 clock, all the even numbered operations are performed and odd are held stable and vere-versa.

Synchronous and Asynchronous Design.

The Sequential Circuits are classified as asynchronous and synchronous based on the timing of their signals.

Asynchronous sequential Cocurt:

1. Output depends on the sequence in which input signals change.

2. Output will get affected whenever the Input Changes

3. Didficult to design.

4. Time delay devices are used as memony clements.

Synchronous sequential circuits

The change of stade occurs only in response to a synchronizing clock pulse.

2. Speed of operation depends on magimum

allowed clock frequency?

3. Clocked flig-flops are used as done wollo of slanges locked tool, ord

longer long Compandinely simples degrapmonogmod fonges find data i (mex) super soprado of

The finite State Machine (Asm) is a type of sequential corcust which of orders great buters sequence through specific patterns of Aniteinstades In a predetermined sequentral manner.

hondshaking protocols to control the data flow Hazards:

Hazards refers to gletches. Those are unwanted swetching transients at the cutput. It is a temporary false-output value in combinational circuit. Self- timed Circuit Designi

Seld-timed circuit design is a digital circuit design methodology where the circuit operate without a certral cleck signal.

Instead of using a global clock to Synchronize all the circuit elements, self-timed carrents use local control signals to allow each component to operate independently and respond to changes in data or input signals.

Procluding reduced power consumpzion, improved

The self timed circuits use the handshalling protocols to control the data flow between the caruff elements.

form persony of the first with the ten exception of a

of rolling Francishing out the contrat. Then

Benefits of Self-tomed corcums:

The benefits of self-tomed circuit design in VISI are:

- 1. Reduced clock distribution complexity

- 2. Improved performance

- 3. Lower power consumption

Dos advantages:

- 1. Design complexity

- 2. Cometed tool Support

- 3. Requires additional circuit control and handshake components.

# INTERCONNECT, MEMORY ARCHITECTURE AND ARITHMETIC CIRCUITS.

#### Interconnects:

The Interconnects play a crucial role in Connecting various components on a chip such as transistors, logic gates, memory cells and other functional blocks.

Efficient Interconnect design is essential

to acheive high performance and low power

Consumption In modern Ic.

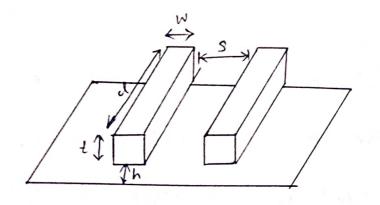

W- Width

1 - Jength

t - threkness

S- Spacing

h. height

Pstch = W + SAspect rateo =  $\frac{t}{W}$

As Inderconnect length increases, its

resistance also increases, leading to voltage drops

and signal degradation. To minimize resistance, wider

and shorter interconnects are preferred.

#### 2. Capacitance (c):

Capacitance 9s the ability of the interconnect to stone charge. It causes delays during charging and discharging, affecting the overall performance of the circuit.

Capacidance Increases with the area and proximity of the adjacent Interconnects. 30, reducing the width or Increasing the spacing between Interconnects can help mittigate capacidance effects.

#### 3. Delay:

Delay is the time taken for a signal to propagate through an interconnect. It is influenced by both resistance and capacitance and is a critical factor in determining the speed of the circuit.

#### 4. Metal Layers:

The number of metal layers and these wordths support the routing density and total wirelength, which inturn affects the overall chips performance and area.

#### 5. Patch:

The pitch is the distance between adjacent metal knes on the same layer.

#### 6. Aspect ratio:

The aspect radio is the radio of the height to the width of interconnect. A ligher aspect radio deads to increased resistance.

7. Cross falk:

Crosstalle is the unwanted coupling of signals between adjacent interconnect. It can cause integrity issues and affects the performance of the circuit.

Electrical wire models:

The clectifical wire models are used to represent the behaviour of metal interconnects that connect various Components on an Ic chip.

These models help designers analyze and predect the performance of anterconnects.

The chorce of the electrical whre model depends on the level of accuracy required for Specific design and the complexity of the interconnect network.

Sequentral Digital corcuits:

The sequential digital circuits are a type of carcuits whose output is based on both current and the previous states.

Designing sequentful considerations of teming, state transitions and synchronous design techniques.

Greneral Design Considerations:

The following aspects are to be kept in mind while designing the sugarential digital circuits:

- 1. Higher reliability

- 2. Lower power dessipation

- 3. lesser cost

- 4. Improved repeatability

- 5. Better performance

## Adders:

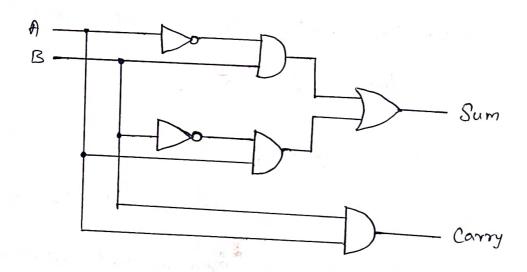

A carculat that adds two bits is called as half odder. A full adder is one that adds three bits.

Half adder:

| A | B | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 6   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1 1 | 0     |

| 1 | 1 | 0   | ,     |

$S = A \oplus B = A'B + AB'$ C = AB full adder:

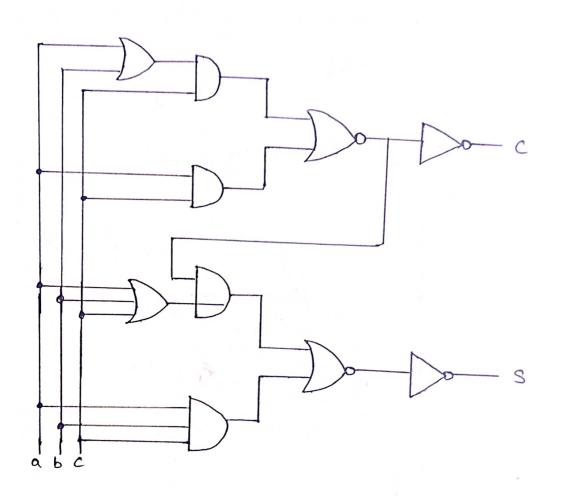

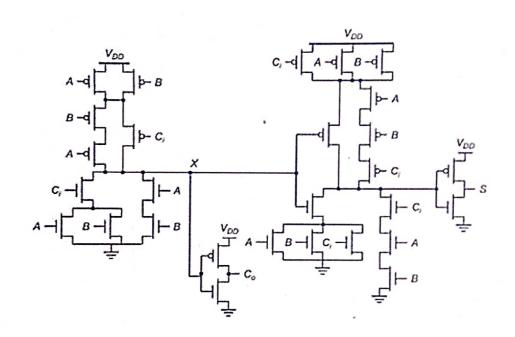

A full adder 9s a combinational circuit

that performs the anthmetre sums of 3 bits.

| a | Ь | C | Sum | Carry |  |

|---|---|---|-----|-------|--|

| 0 | 0 | 0 | 0   | O     |  |

| 0 | 0 | 1 | 1   | 0     |  |

| 0 | 1 | 0 |     | 0     |  |

| 0 | 1 | 1 | O   | )     |  |

| 1 | O | O | 1   | 0     |  |

| 1 | 0 | 1 | 0   | ,     |  |

| 1 | 1 | O | 0   | )     |  |

| ) | 1 | 1 | 1   | 1     |  |

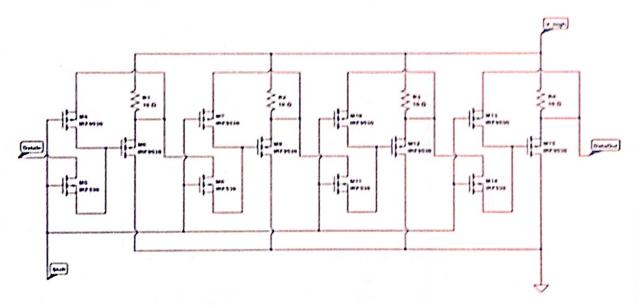

The above mentioned full adder can be constructed using the pmos and NMOS transisters also which can be implemented in VISI. This alternative implementation needs 28 transistors which looks like this.

Here,

Sum = a D b D C

Carry = ab + c (a Db)

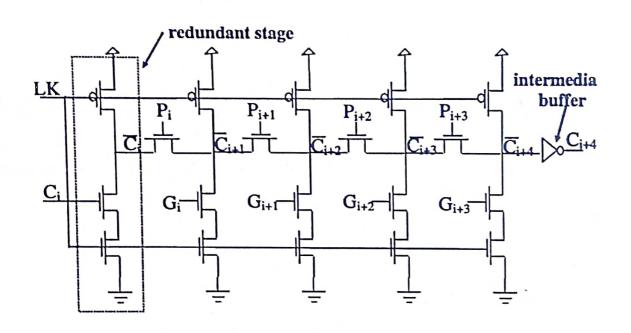

Ripple carry adder:

The basic principle of a ripple carry adder is to add two binary numbers bit by bit,

Starting from LSB to the MSB. Each stage consists of a full adder, which takes 3 inputs. It produces a outputs, the sum and carry, which is propagated to the next stage.

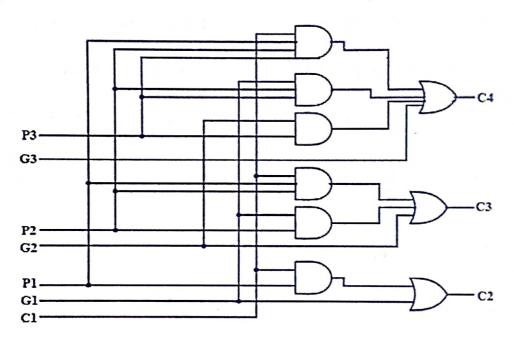

Carry Look - Ahead adders:

whole the rapple carry adders are generally avoided simple to implement, they are generally avoided in high speed or high performance carriers.

In such cases, the to carry look ahead adders are preferred due to the reduced propagation delays and improved performance.

The carry look ahead adder uses the parallel carry computation technique to overcome the propagation delay.

The carry look ahead adder reduces the dependency on carry propagation from one stage to another, resulting in Laster addition of numbers compared to ripile carry adder.

One of the key advantages of this adder is that it has constant time delay.

## Carry 929 adder:

The carry sign adder or carry bypass adder Combines the advantages of both ripple carry adder and carry look ahead adder to provide a good trade-off between the speed and area effectioney.

This method divides the carry skip.

adder into several small blocks each with Hs

own carry look-ahead logge. This allows the adder to perform multiple carry computations in parallel and then scient the correct carry value based on the final sum.

Manchester Carry-chain Adoler;

The manchester carry chain adder see uces a unsque approach to generate carry signals. It uses a chain of XOR gates that are used to propagate carry signals from one block of hits to the next.

This faster propagation of carry signal reduces the overall propagation delay of the adder. However, this uses more orea when companed to the other odder making the choice difficult for the designers.

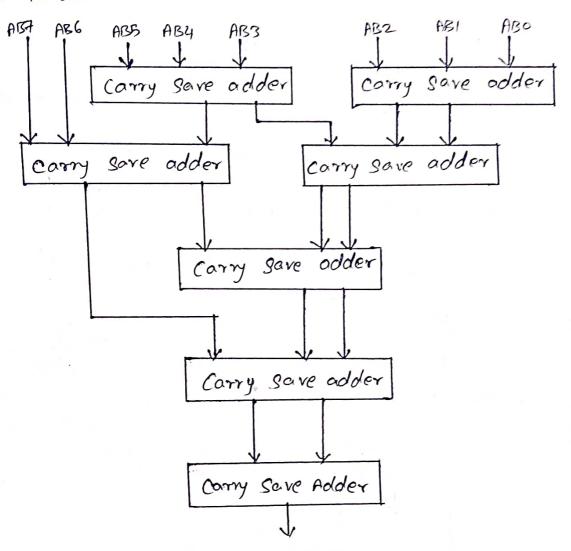

### Multipliers!

There are Several types of multipliers in VLSI circuists, each with its advantages and applications.

#### Binary multiplier:

It is a simplest form of a multiplier which performs the multiplication using the basic and logger gates.

#### Wallace Tree multiplier:

The wallace tree multiplier uses a tree based structure to generate partial products in parallel

parallel, reducing the number of adders required.

This leads to better speed and area efficiency

for moderate bit width multiplication.

Here, ABO to ABT represents the partial products. The wallace multipliers consists of AND gates, carry save adders and carry propagate adder. Here, all the partial products are added at the same time instead of adding one at a time.

## Comparator:

The comparator is a corcuit which is used to compare the magnitude of two bynony numbers.

The base operation of a comparator involves comparing the corresponding bits of two benany numbers and generating output to andica Whether one number is greater than, equal to or less than the other number.

## Shiff Registers:

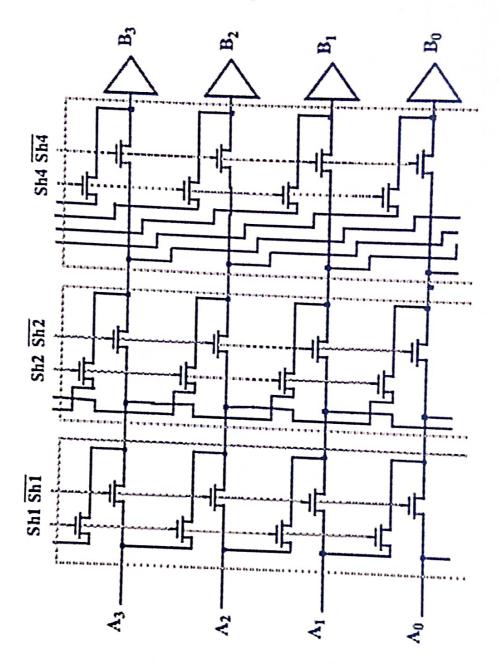

The shift negasters one used to shift the word to left or right over the position desared by the user.

#### Barrel Shiller:

n barrel Shirter has nedara inputs,

nedarla outputs and a soil control input that

Specify how to shirt the data between

Proport and output.

The various shift operations that can

be personned in shirt registers are!

- 1. log@al right shild

- 2. Left sheft

- 3. Arithmetic right shift

- 4. Arithmetic left shift

- 5. Rodoste.

Logarithmic Shifter:

In this, the speed of the n-bit shifte, is proportional to log(n)

Hence it can provide faster shifting operations. It uses stages of multiplexers which decompose the shift into power of two stages.

The bornel glasser is better for small glassers and the log slasser is preserved for the Jarger ghassers hoth due to saze and delay.

Logse Implementation using Programmable Devices:

The programable legge derices (PLD) are the standard se, that can be programmed to simplement the dossinal functions. The important fearlunes of PLD are:

- 1. No customized mask layers

- 2 fast design lum around

- 3. A single large block of programmable inder connect

- 4. A modine of logic macro cells.

The different types of PIDs are read-only memory (Rom), Programmable concy logic (PAL) and programmable Logic anal (PZA).

Road only Memory (Rom):

The Rem is the simplest type of programmable and which can be used to , once to store binary data.

The most commonly used types of Remuse as metal fuse that can be blown remonently (promently programmable Rom or Eprom uses a programmable mos transistors whose characteristies are altered by applying a high voltage.

A masked Rom is a regular array of transistors permanently programmed using custom mask patterns.

Programmable Logic Array (PLA):

A PLA 83 Similar to a Rom. In Pla, a

Set of programmable AND and OR planes are there.

They both are programmable and used to simplement

Combinational logic circuits.

3- Input variables 23- 8 programmable AND gate 4. Programmable OR gates

A P2A has 2N AND gates for N Empured Variables and M or gailes for m Empuroudparts, each of Which can be programmed to generate a product form of Empury variables.

A size of PIA is specified by the number of inpuls, no. of product terms & outputs.

programmable. The PLA reduces the chip area and it is Nexable.

The dissadvantage of PLA is that 945 propagation delay is more and it is limited to functions that can be expressed in sop form.

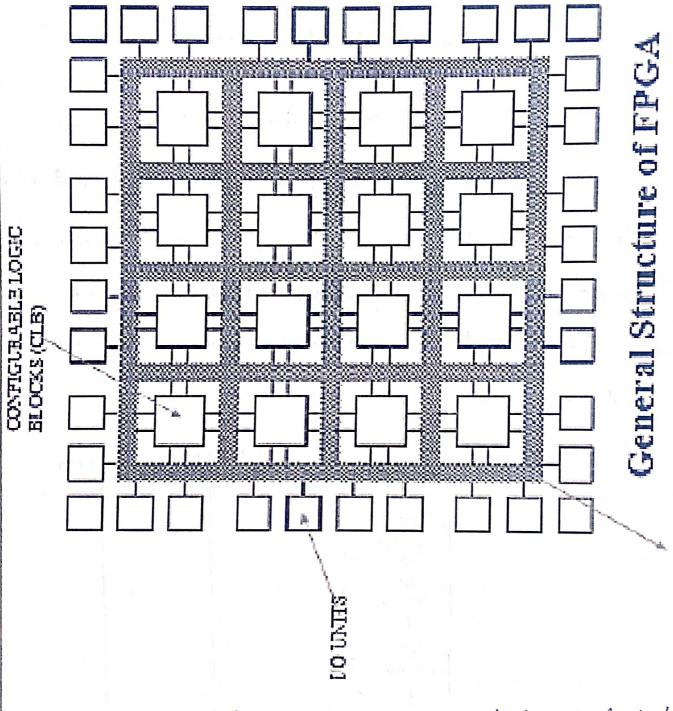

#### FPGA:

FPGA 98 a field programmable Gate Array.

It is a type of programmable legge dence used in degital carcust design and prototyping. The key features of FPGA are:

- 1. Configurability

- 2. Look up table

- 3. Programmable Interconnect

- 4. HPgh parallelism

- 5. Partial reconfiguration

- 6. HDL Implementation.

Melo

The FPLA has a set of Amput & output blocks which are configured as fixed Alp, & output.

interconnection Network

The basic architecture of FPGA consist

Of:

- 1. Configurable logic Block (CLB)

- 2. I/o block

- 3. Programmable interconnect.

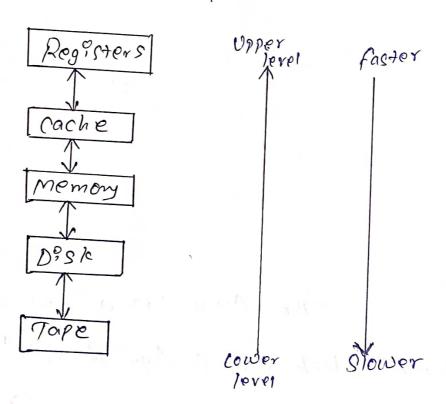

Memory Architecture and Building Blocks:

The memory architecture refers to

the organization and hierarchy of memory

components in a computer system. It defines

how data and instructions are stoned, acressed

and managed within the system.

The data storage devices of various sizes are required for most 20 designs. A collection of storage cells together with ascociated Gruins are needed to transfer information in and out of the device.

Memory element terminology:

#### Latch:

Latches are transparent while the indernal memory is being set from input data.

#### flip - flop:

The flip-flops are not transparent - reading input value and changing its output one Seperate events.

## Types of memory:

Mony types of memory derices are avoilable for use in modern computer system.

The Random Access memory 9s a memory array with individual bit access and has both read and write capabilities.

The read only memory has no write capabilities.

## flash Memory:

The entree content in the flagh memory can be erased by less than a second. The erasing process is done by an electric pulse and hence it is also called flash EEPRom. It is a non-volatile memory.

|                     |           | (         | 1             | ٠.        | 1        |                          |                              |             |

|---------------------|-----------|-----------|---------------|-----------|----------|--------------------------|------------------------------|-------------|

| Speed               | fast      | Moderate  | forst         | fast      | Fast     | Read-fast<br>Witte-81000 | Read - fast<br>Witte - 81600 |             |

| (0St (Per byte)     | Expensive | Moderate  | Inex pensive  | Moderoite | Moderate | Ex ponsive               | Medesade                     | 5 momal o   |

| Max Erase<br>Cycles | Unlemoted | Unlimited | W/A           | A/W       | L'imited | Lomoteel                 | Compted                      | momon       |

| Erase<br>S92e       | Byte      | Byte      | M/W           | A/54      | Entire   | Byte                     | Sector                       | Varous      |

| Wrfteable           | Sox       | 50%       | N°            | Once      | Sah      | Soh                      | yes                          | Lo nosmodmo |

| Volatile            | səh.      | sak       | NO            | 20        | .NO      | No                       | No                           | Com'        |

| Type                | SRAM      | DRAM      | Masted<br>Rom | PRom      | EPROM    | EEPROM                   | Flash                        |             |

|                     |           |           |               |           |          |                          |                              |             |

These building blocks work together to form the memory systems with different capacities, across times and functionalities.

## UNIT - 5

# ASIC DESIGN AND TESTING

Introduction to water to chip fabrication process.

The Ic fabrication is a sequential and a lengthy process. The various steps involved in Ic fabrication process are:

A. Ingo of other

- 1. Water preparation

- 2. Oxidation

- 3. Diffusion

- 4. Jon implantation

- 5. Chemical vapour deposition

- 6. Metal ? 20450n

- 7. Phoblithography

- 8. Packaging

#### Stop- 100 to set settled in the same of the

Processing is done on a thin film of pure silecon Crystal. P-Impunities are introduced as crystal.

The typical water diameter 95 75 to 150 m and thechness 95 0.4 mm. The impurity 95 boron howing concentrations of 1018/cm3 to 1016/cm3 giving resistivity of 25 D.cm to 252-cm.

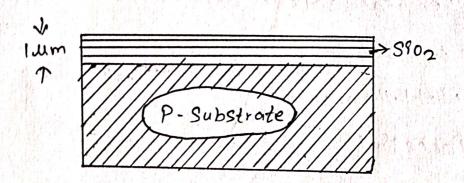

#### Step. 2!

A loyer of Silicon disoxide (3902) is grown over the Surface of water for protection of Surface. The thickness of 5902 95 1 um.

This layor acts as barrier to departs during processing.

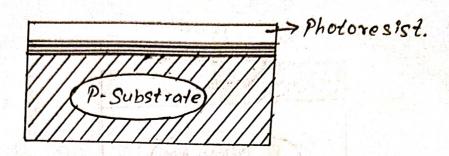

#### Step-3:

The sion layer is now covered with Photo resist which is deposited on water.

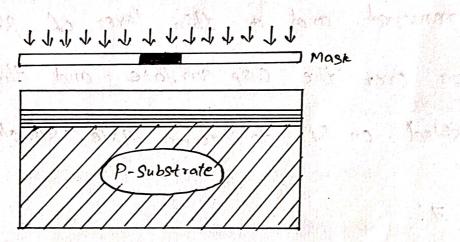

SHEP 4:

The photonesist layer is exposed to UV light through a mast. The mast Corresponds to regions into which diffusion takes place.

Step - 5:

These regions are then etched tegether so that water is exposed in window defined by mark.

Control of the contro

The photoresist layer remains on substrates and the strates and the strates and the polysilicon is deposited on it to form gate structure.

Step 7:

The diffusion is acheined by heating the worder to high temperature and passing n-type impurity

oror st

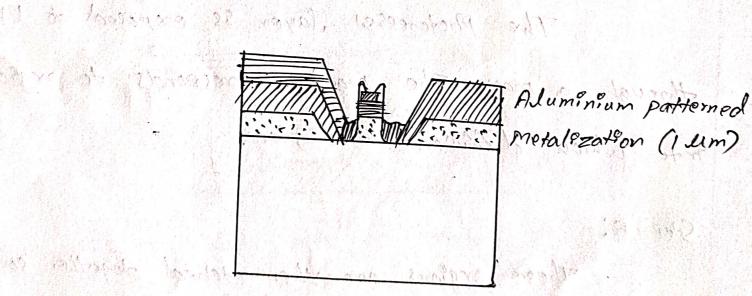

Over the Surface. The S802 layer is grown and masked with photopessed and then exched to expose specific areas of polysilicon. The waster is then metal deposited over its surface to a thickness of hum. The metal is usually aluminium.

Mecrochip Design Process:

Ozidation:

During the process of It Pobrication when solicion is exposed to exygen or water vapour at high temperature to form a continuous layer of 5902 is called as thermal or wet explation.

Crthography:

Lithography is a process of transferring patterns of geometric shapes in a masse to a layer

of radiation sensitive moderial for covering surface of semiconductor water.

## Diffusion:

The process of antroducing controlled amounts of dopants anto semiconductors is called diffusion. It is carried out in furnace where anert gas containing dopant is pass through the water at temperature range 800 to 1200°C.

# Ion Implandation:

The process of introducing high energy charged particles into the Substrate is called as fon implandation.

The same of the same of the

#### Metall9zation:

Medallization 9s a process of formation of metal films for interconnections, Chimic contacts and rectifying metal semiconductor Contacts.

Issues in test and verification of complex chas:

Some of the major issues includes:

1. Design Complex Hy:

Complex chips contain millions of transistors and introde interconnections. As a result, the test and verification process become more difficult.

2- functional verification:

Ensuring that the chip functions correctly according to its specifications is a major challenge.

3. Timing & Synchronization:

As chips become faster, dealing with timing issues and ensuring proper synchronization between different components is challenging.

4. Power constraints:

Testing & verificate verytying a chip adhering

to the power limits require sophisticated (est

## 5. Test Access:

The lemited number of took pans can lend to difficulty an observing and controlling internal signals during testing.

March 18 - 18 March 1

# 6. Security Concerns:

Ensuring the chips registance to attack, like reverse engineering and scale channel, attacks adds an additional complexity to the vertication process.

The automated testing and verification tools help suprove the efficiency and coverage of the testing process.

Contract of the second

Testing and Logic verition:

The cmos Ic tests can be categorized as:

- 1. Functionality dost

- 2. Silicon debug

- 3. Manufacturing test.

The functionality test venifies that the chip performs its intended function. The solpcon debug tests helps in finding the manufacturing faults. in solicon area.

The manufacturing tests verify that every transistor, gate and storage elements in the chip functions correctly.

Logic Vontication:

Chip functional testing is done by simulation.

The chip simulation is usually done at HDZ level.

The reinfocation engineers write test bench for HDZ.

The bug tracking system is an important and tool to use during ventication. It allows to man a wide variety of bugs.

Application Specific Ica (ASICA)

Applecation Specific Integrated circuit

95 a full- custom corcult on which every mask of

defined by the customer or a semo-custom corcuit

Where only few masks are defined.

Ask 98 custom designing Ic for a particular application such as processing unit of a mobile phone. Asic 95 useful for high volume production.

ASICS are commonly used in various

Industries such as telecommunications & Automotives.

The design process of Asic is complex and costly.

S O S A C.

But the benefits of tailored performance and efficiency overweigh the Pnitial Pniestment for certain mission - critical applications

## Advantages:

- 1. Better performance.

- 2. More secure for design carcuit

- 3. compact

- 4. Contains digital as well as analog corcusts.

## Disadvantages:

1. Cannot be easily replaced 91 damaged.

2. Costly.

### Types of Asica:

- 1. Full custom ASIC

- 2. Sem? custom Asic

ASIC Design flow is a series of steps methodologies involved in Asic. It has following tey stages:

1.8.

- 1. Specification and Archidecture

- 2. Design entry

- 3. RTL Design

- 4. Functional ventication

- 5. Synthesis

- 6. Physical design

- 7. Design for test

- 8. Toming closure

- 9. Tapeout

- 10. fabrication and testing

- 11. Packaging and System

#### Test Bench:

In the Asic test bench, the user defines the input stimuli and expected outputs to stimulate

- DISA WESTERN KING

The ye

the design under test. The test bench monitors the responses generated by ASIC and companies them to the expected outputs to check for correctness.

The test bench can be written 9m 14D2

like verilog or VHDL or 9m specialized verification

languages like system verilog.

Writing the test benches in Verilog HD2:

A test bench allows you to smulate and venty the functionality of your design before moving on the actual hardware implementation.

The procedure to write a test bench using Venlog HDZ 95:

WARREN ?

- 1. Module declaration

- 2. Instantiate the DUT (Design Under Test)

- 3. Define Inpuls

- 4 Apply anguas

- 5. Monitor outputs

- 6. Samulate & Lun

- 7. Analyse nesuts

```

A simple example of verilog test be

for an AND gote:

module tb-and-gate;

11 declare Input and output

Signals

rega,b;

wire y;

11 Instantiate the design under Test (DUT)

and gate and inst (a(a), b(b), y(y));

11 Apply Super Stimuli Eniteal begin

& desploy ("Testing and gate ...");

a=0; b=0;#5;

a=0; b=1; #5;

a=1; b=0; #5;

a=1; b=1; #5;

& finish;

end

//monstor outputs

always Q(y) & display (" output y = 1.6", y);

```

endmodule

# Automatic Tost Pattern Generalion:

Automatic test pattern honoration (ATPG)

is a process used to automatically create the

test patterns that can be used to test the

functionality and reliability of Ic.

The goal of ATPA of to generate the test partierns that can detect the manufactioning defects. It uses various algorithms to expresent generate the test partierns ensuring high Pest Coverage fault detection.

Design for Testability:

The design for destablishy covers

three Important approaches:

- 1. Ad-hoc testing

- 2. Scan based approaches

- 3. Self and built-in test

Adhoc testing:

The Adhor testing is a dynamic desting approach where the tester explores the functionality of the design and identifies the potential defects based on their own understanding or intuition.

Adhoc testing can be useful for quickly discovering certain issues like identifying the defects.

Some of the ad hoc testable dosign dechniques are:

- 1. Partition and Muse technique

- 2. Inidialize Seavential Orcust

- 3. Disable internal clocks

- 4. Avosd Asynchronous Cosse

- 5. Avoid delay dependent losse

Ad hoc methods were the first DFT techniques individuced in 1970s. The goal was to target only those portions of carcuit that would be difficult to tost and add circuity to improve the controllability and observability.

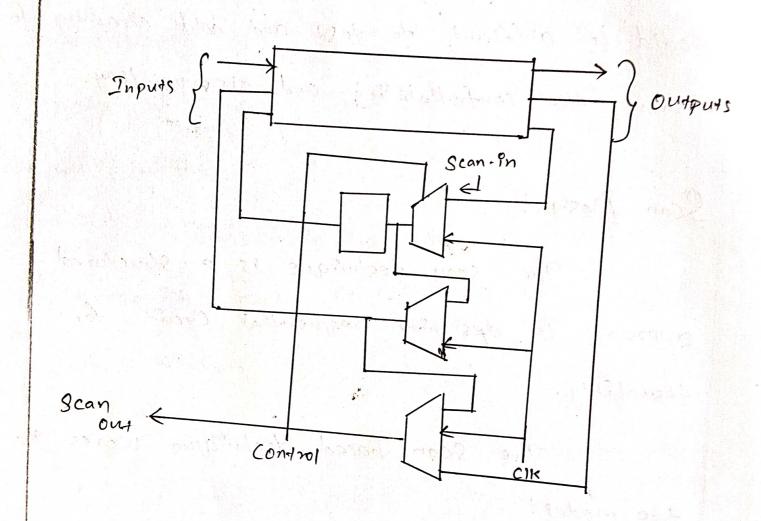

Scan Design:

The scan technique is a structured approach to designing sequentral circuit for testability.

The scan based technique works In two modes:

- 1. Test mode

- 2. Normal mode

In test mode, the scan-in signal is clocked into scan path and output of last stage is scanned out.

In normal mode, the scan in disabled and the carcuit functions of sequentral Arcuit.

Boundary Scan Check:

Boundary scan check has the following advantages over other pesting methods:

- 1. Increased fault corrage

- 2. Time efficient.

the Shift register during operation. Bedfreithon Scan ougliber Boundary Scar Boundary 1045 6 Bar ▶ Boundary 4 BSR Boundary Stan Regiller Input 1 stockede pan Internol Logge Brewity BSB Scan Scan out BSR

- 3. Simple

- 4. Accurate and efficient.

Boundary Scan Standards:

Several Standards are Sperified to boundary Scan Check testing. Their prime Objective 45 to ensure testing and development loss costly and effection. Some of the boundary Scan Standards are:

- 1. Jognt test Action group (JTAG 1988)

- 2. Flomend test & maindanance (ETM VHSIC)

- 3. VHSIC Test and Maintenance Bus Standard

- 4. Testablisty Bus standard (SEEE 1989/JEEE 1149.1)

Boundary Scan test Methodology:

The boundary Scan shift register

provents output from reppleng as data es shifted

The test set is scanned into boundary scan register (BSR) by using a scan in part with test stimula input. The response of the circuit is captured in parallel by BSRs in Series and scanned out through scan out part.

The boundary scan path is having serial enput output cells and has appropriate clock pads. The cells or pads are provided for:

- 1. Interconnections between chips

- 2. Internal Self dest

The various tests that are carried out by the architecture IEEE 1149 are:

- a) sampling & setting this Input and outputs

- b) connectarity between test components

- C) Destribution and collection of Self test and build en test mosulis

The BIST is used to renty the functionality and integrity without relying the external test equipments. It involves incorporate specific test circuits within the system to perform self diagnostic checks.

The advandages of BIST are:

- 1. Cow cost

- 2. High quality testing

- 3. faster fourt detertion

- 4. Eage of dragnostes

- 5. Reduced maintenance & repair costs

The essential modules required for B197 are:

- 1. Pseudo random partiern Generator

- 2. Output response Analyser.

IDDOV Testing:

IDDA testing is used to identify the defects in Ic by measuring the quiescent supply current when the circuit is in a stable state with no inputs changing.

During this test, the Ir is placed in a low power mode, an where it is not actively processing any signals and IDDA current is measured.

The IDDA test is performed by applying the test vector and then monitoring the current drawn from the power supply. This test negulinos more time but fault detection capability as greatly improved.

The design guidelines for IDDA testability ano.

- 1. Low static current states

- 2. No active Pull-ups/pull-downs

- 3. No Internal drive conflicts

- 4. No floating nodes

- 5. No degradod voltagos.